01_I.MX6U芯片简介

目录

I.MX6芯片简介

Corterx -A7架构简介

Cortex-A处理器运行模型

Cortex-A 寄存器组

IMX6U IO表示形式

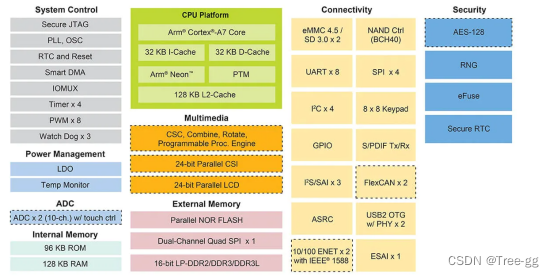

I.MX6芯片简介

ARM Cortex-A7内核可达900 MHz,128 KB L2缓存。

并行24bit RGB LCD接口,可以支持1366*768分辨率。

3.8/10/16位 并行摄像头传感器接口(CSI)。

4. 2个MMC 4.5/SD 3.0/SDIO 接口

5. 2个USB 2.0 OTG, HS/FS, Device or Host with PHY.

6.音频接口3x 12S/SAI, S/PDIF Tx/Rx.

7.2个IEEE802.3标准10/100Mbps以太网接口。

8. 多达8个UART接口。

9.2个12-bit ADC最高支持10个输入通道,支持电阻触摸屏(4/5线)。

10,安全模块: TRNG, Crypto Engine(AES with DPA, TDES/SHA/RSA), Secure Boot。

Corterx -A7架构简介

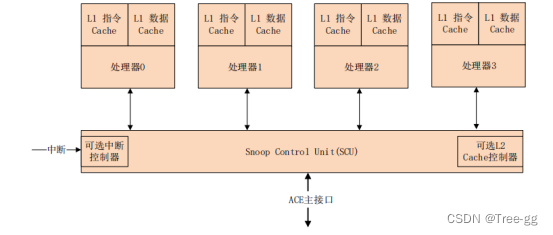

Cortex-A7 MPcore处理器支1-4核,通常是和Cortex-A15组成big.LITTLE架构的,Cortex-A15 作为大核负责高性能运算,比如玩游戏啥的,Cortex-A7负责普通应用,因为 CortexA7省电。Cortex-A7本身性能也不弱,不要看它叫做Cortex-A7但是它可是比Cortex-A8性能要强大,而且更省电。ARM官网对于Cortex-A7的说明如下:

“在 28nm 工艺下,Cortex-A7可以运行在1.2-1.6GHz,并且单核面积不大于 0.45mm2(含有浮点单元、NEON和 32KB的 L1缓存),在典型场景下功耗小于100mW,这使得它非常适合对功耗要求严格的移动设备,这意味着Cortex-A7在获得与Cortex-A9相似性能的情况下,其功耗更低”。Cortex-A7 MPCore支持在一个处理器上选配1-4个内核, Cortex-A7 MPCore多核配置如图:

Cortex-A7MPCore的L1可选择8KB, 16KB, 32KB, 64KB, L2Cache可以不配,也可以选择 128KB、256KB、512KB、1024KB。IMX6UL 配置了 32KB 的 L1 指令 Cache 和 32KB 的L1数据Cache,以及128KB的L2Cache。 Cortex-A7MPCore使用ARMv7-A架构,主要特性如下:

1.SIMDv2扩展整形和浮点向量操作。

2.提供了与ARM VFPv4体系结构兼容的高性能的单双精度浮点指令,支持全功能的IEEE754

3.支持大物理扩展(LPAE),最高可以访问40位存储地址,也就是最高可以支持1TB的内存。

4.支持硬件虚拟化。

5.支持Generic Interrupt Controller(GIC)V2.0。

6.支持 NEON,可以加速多媒体和信号处理算法。

Cortex-A处理器运行模型

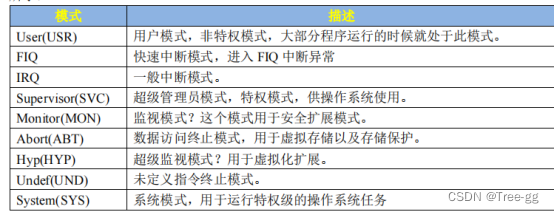

以前的ARM 处理器有7中运行模型:User、FIQ、IRQ、Supervisor(SVC)、Abort、Undef和System,其中User是非特权模式,其余6中都是特权模式。但新的Cortex-A 架构加入了TrustZone安全扩展,所以就新加了一种运行模式: Monitor,新的处理器架构还支持虚拟化扩展,因此又加入了另一个运行模式; Hyp,所以Cortex-A7处理器有9种处理模式,如表

在表中,除了User(USR)用户模式以外,其它8种运行模式都是特权模式。这几个运行模式可以通过软件进行任意切换,也可以通过中断或者异常来进行切换。大多数的程序都运行在用户模式,用户模式下是不能访问系统所有资源的,有些资源是受限的,要想访问这些受限的资源就必须进行模式切换。但是用户模式是不能直接进行切换的,用户模式下需要借助异常来完成模式切换,当要切换模式的时候,应用程序可以产生异常,在异常的处理过程中完成处理器模式切换。当中断或者异常发生以后,处理器就会进入到相应的异常模式种,每一种模式都有一组寄存器供异常处理程序使用,这样的目的是为了保证在进入异常模式以后,用户模式下的寄存器不会被破坏。

STM32 和 UCOS、FreeRTOS就会知道,STM32 只有两种运行模式,特权模式和非特权模式,但是Cortex-A就有9种运行模式。

Cortex-A 寄存器组

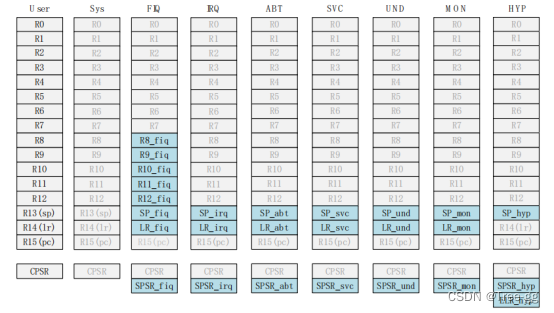

ARM 架构提供了16个32 位的通用寄存器(RO-R15)供软件使用,前15个(RO-R14)可以用作通用的数据存储,R15是程序计数器PC,用来保存将要执行的指令。ARM 还提供了一个当前程序状态寄存器 CPSR 和一个备份程序状态寄存器 SPSR,SPSR 寄存器就是 CPSR 寄存器的备份。这18个寄存器如图所示:

Cortex-A7有9种运行模式,每一种运行模式都有一组与之对应的寄存器组。每一种模式可见的寄存器包括15个通用寄存器(RO-R14)、一两个程序状态寄存器和一个程序计数器PC。在这些寄存器中,有些是所有模式所共用的同一个物理寄存器,有一些是各模式自己所独立拥有的,各个模式所拥有的寄存器如表所示:

从图中浅色字体的是与User模式所共有的寄存器,蓝绿色背景的是各个模式所独有"的寄存器。可以看出,在所有的模式中,低寄存器组(R0-R7)是共享同一组物理寄存器的,只是一些高寄存器组在不同的模式有自己独有的寄存器,比如FIQ模式下 R8-R14是独立的物理寄存器。假如某个程序在FIQ模式下访问R13寄存器,那它实际访问的是寄存器R13_fiq,如果程序处于 SVC 模式下访问R13 寄存器,那它实际访问的是寄存器 R13_svc。总结一下,CortexA 内核寄存器组成如下:

1.34个通用寄存器,包括R15程序计数器(PC),这些寄存器都是32位的。

2.8个状态寄存器,包括CPSR和SPSR。

3.Hyp模式下独有一个ELR_Hyp寄存器。

IMX6U IO表示形式

STM32,管脚名字: PAO-15, PBO-15 PC,PD…

I.MX6ULL:管脚名字:PAD_BOOT_MODEO 管脚的复用:

VIOMUXC_SNS_SW_MUX_CTL_PAD_BOOT_MODEO MUX复用功能的意思

IOMUXC_SNVS_SW_PAD_CTL_PAD_BOOT_MODEO

对于6ULL,查看管脚复用的步骤:

1.打开参考手册

2.找到32章,IO复用章节

3.查找对应的管脚