SerDes介绍以及原语使用介绍(1)OSERDESE2

文章目录

- 前言:为什么需要serdes

- 一、OSERDESE2框图

- 二、OSERDESE2端口信号

- 二、OSERDESE2原语参数

- 三、OSERDESE2时序

- 3.1、SDR模式

- 3.2、DDR模式

- 3.3、DDR模式下三态传输

前言:为什么需要serdes

需要 SerDes(串行器/解串器)主要是为了应对高速数据传输和复杂系统集成的挑战。以下是具体原因和应用场景:

-

高速数据传输

数据带宽需求增加:随着数据处理能力的提升,系统对数据传输带宽的需求不断增加。SerDes可以实现更高的传输速率,满足带宽需求。

时钟频率提升:串行传输能够以更高的时钟频率工作,从而提高数据传输速度。 -

减少引脚和布线

引脚数量减少:在并行传输中,需要多条数据线和相应的引脚。SerDes通过串行化数据传输,显著减少了所需的引脚数量。

布线复杂性降低:减少了PCB上的布线数量,简化了设计,降低了成本和干扰。 -

改善信号完整性

降低串扰和噪声:并行传输中,信号线之间的干扰和噪声是一个主要问题。串行传输减少了这些问题,提高了信号的完整性。

长距离传输:串行信号在长距离传输中更容易保持信号的完整性,适用于芯片间和板间通信。 -

节省空间和功耗

减少芯片面积:通过减少I/O引脚的数量,SerDes可以帮助节省芯片的面积。

优化功耗:尽管SerDes电路本身可能功耗较高,但整体系统的功耗效率会因为减少并行I/O而得到优化。 -

适应现代系统需求

支持多种标准和协议:SerDes广泛应用于各种高速接口标准,如PCI Express、SATA、USB、以太网、光纤通道等,适应不同的应用需求。

系统集成:现代系统越来越复杂,需要将多个子系统集成在一起。SerDes能够高效地实现不同模块间的数据传输和通信。 -

灵活性和可扩展性

动态带宽分配:SerDes能够根据需要动态分配带宽,提高系统的灵活性。

可扩展性:可以通过增加SerDes通道的数量来扩展系统的总带宽,满足未来的需求。

应用场景

- 通信网络:用于高速网络接口,如以太网和光纤通道。

- 存储系统:如SATA、SAS等存储接口。

- 计算机总线:如PCI Express、USB等系统总线。

- 多媒体接口:如HDMI、DisplayPort等视频和音频接口。

- 芯片间通信:如在多芯片模块(MCM)和系统级封装(SiP)中使用。

- 板间通信:用于不同电路板之间的高速数据传输。

总结:

需要SerDes的主要原因在于其能够大幅提升数据传输速率、减少引脚数量和布线复杂性、改善信号完整性、节省空间和功耗,以及满足现代高速系统的需求。通过串行化和解串化,SerDes在各种高速数据传输和复杂系统集成场景中发挥着关键作用。

而我们之前学习的GT(包括GTX、GTH和GTP):是Xilinx在高速SerDes的基础上,增加了其他模块,如8b/10b编解码等(具体可以看Xilinx相关文档,如ug476)形成的一个高速串行收发器,GT是Gigabit Transceiver的意思,它是实现当下一些高速串行接口的基础:如PCIe、RapidIO等

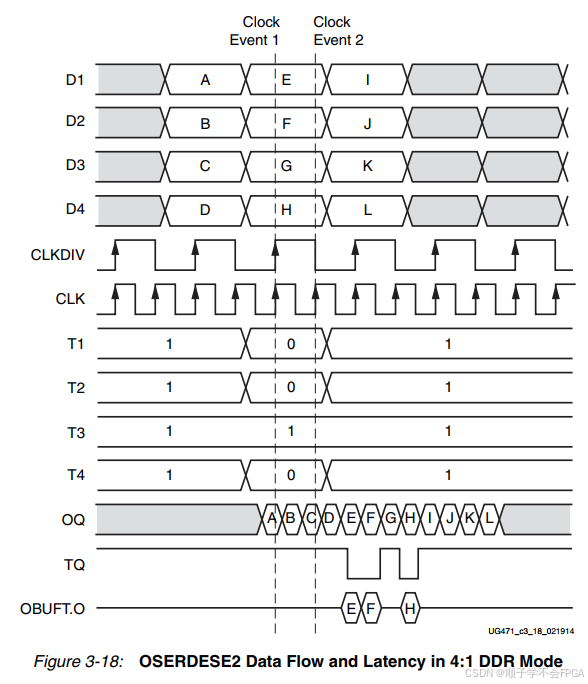

一、OSERDESE2框图

参考:xilinx ug471手册

上图所示,OSERDESE2(Output Parallel-to-Serial Logic Resources)是7系列FPGA器件中的专用并串转换器,具有特定的时钟和逻辑资源。每个OSERDESE2模块都包含一个用于数据和三态控制的专用串行器。数据和三态串行器输出都可以配置为SDR(在时钟的单沿传输数据)和DDR(在时钟的双沿传输数据)模式。数据序列化最高可达 8:1(如果使用OSERDESE2宽度扩展,则为10:1或14:1)。

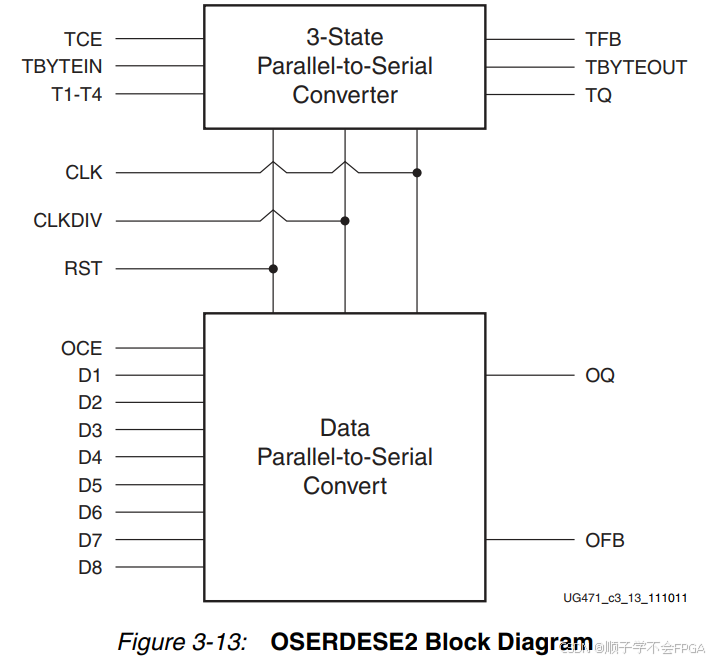

二、OSERDESE2端口信号

- CLK:与输出串行数据对齐的高频时钟信号

- CLKDIV:与输入并行数据对齐的低频时钟信号

- D1-D8:并行输入数据端口,一个OSERDESE2最多配置8位输入并行输入数据,两个OSERDESE2模块通过级联可以配置10位或14位并行输入数据。其中D1最先转换为串行数据输出。

- OQ:串行信号输出,直接与IOB相连,输出到FPGA管脚,若是需要将串行信号输出到2. ODELAYE2或者ISERDESE2,那么使用OFB端口,OFB和OQ两个端口的信号一模一样,只是数据走向不同。

- T1-T1:OSERDESE2原语还有三态控制输出的功能,那么T1-T4是三态控制信号,与D1-D4数据对应。使用三态功能时,TQ作为串行输出的管脚,用于判断OQ信号此时是作为输入引脚(TQ为高电平)还是输出引脚(TQ为低电平),而TFB与OFB原理类似。

- OCE:数据并串转换的时钟使能信号。

- TCE:三态转换的时钟使能信号。

- RST:是一个异步的高电平复位,RST拉高时,会将CLK和CLKDIV时钟域下的所有触发器清零输出低电平。当设计中存在多个OSERDESE2模块时,推荐所有OSERDESE2均使用同一个复位信号,并且RST拉高应该与CLKDIV信号同步,确保所有OSERDESE2模块能够同时退出复位状态。

- TBYTEIN、TBYTEOUT:信号是用于DDR3控制器使用的,直接关闭即可。

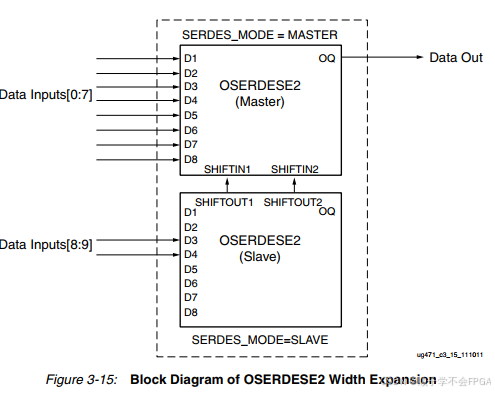

- SHIFTIN1、SHIFTIN2、SHIFTOUT1、SHIFTOUT2:用于OSERDESE2转换数据时的位扩展,单个OSERDESE2最多只能将8bit并行数据转换位串行数据输出,而两个OSERDESE2级联最多可以将14bit并行数据转换位串行数据输出。如下图所示,是两个OSERDESE2将10bit并行输入转换为串行输出的连接框图。从OSERDESE2的SHIFTOUT1、SHIFTOUT2连接到主OSERDESE2的SHIFTIN1、SHIFTIN2实现扩展。Slave OSERDESE2模块的输入数据从D3开始连接,D1和D2不能使用。

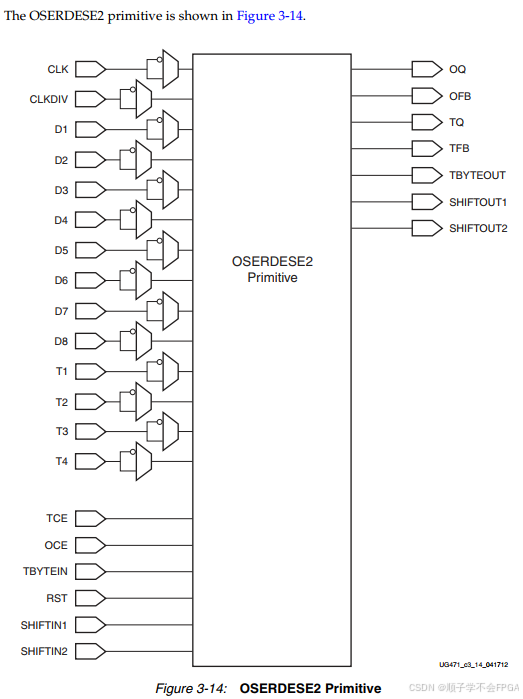

二、OSERDESE2原语参数

OSERDESE2 #(.DATA_RATE_OQ("DDR"), // DDR, SDR.DATA_RATE_TQ("DDR"), // DDR, BUF, SDR.DATA_WIDTH(4), // Parallel data width (2-8,10,14).INIT_OQ(1'b0), // Initial value of OQ output (1'b0,1'b1).INIT_TQ(1'b0), // Initial value of TQ output (1'b0,1'b1).SERDES_MODE("MASTER"), // MASTER, SLAVE.SRVAL_OQ(1'b0), // OQ output value when SR is used (1'b0,1'b1).SRVAL_TQ(1'b0), // TQ output value when SR is used (1'b0,1'b1).TBYTE_CTL("FALSE"), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC("FALSE"), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH(4) // 3-state converter width (1,4))

OSERDESE2一共有11个参数,分别如下:

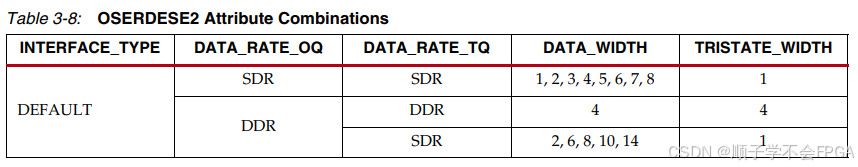

- DATA_RATE_OQ:定义数据是以单数据速率(SDR)还是双数据速率(DDR)进行串行化处理,默认值为DDR。

- DATA_RATE_TQ:定义是否将三态控制作为单数据速率(SDR)还是双数据速率(DDR)进行处理。该属性允许的值为SDR、DDR或BUF,默认为DDR。在SDR和DDR模式下,使用T1~T4输入,并且可以使用TRISTATE_WIDTH配置三态输入宽度。在BUF模式下,SDR和DDR模式寄存器被旁路,使用T1输入。

- DATA_WIDTH:定义并串转换器的并行数据输入宽度。当 DATA_RATE_OQ设置为SDR时,DATA_WIDTH可能取值为2、3、4、5、6、7和8。当DATA_RATE_OQ设置为DDR时,DATA_WIDTH属性的可能值为 4、6、8 、10 和 14。

- INIT_OQ:表示OQ信号的初始状态,默认为1’b0。

- INIT_TQ:表示TQ的初始状态,默认为1’b0。

- SERDES_MODE:定义使用宽度扩展时OSERDESE2模块是主模块还是从模块。可以为MASTER或SLAVE,默认为MASTER。

- SRVAL_OQ:表示OQ信号复位时的值,默认为1’b0。

- SRVAL_TQ:表示TQ信号复位时的值,默认为1‘b0。

- TBYTE_CTL:用于DDR3控制器使用

- TBYTE_SRC:用于DDR3控制器使用

- TRISTATE_WIDTH:定义三态控制并串转换器的并行三态输入宽度。当DATA_RATE_TQ设置为SDR或BUF时,TRISTATE_WIDTH属性只能设置为1。当DATA_RATE_TQ设置为DDR时,TRISTATE_WIDTH属性的可能值为1和4。

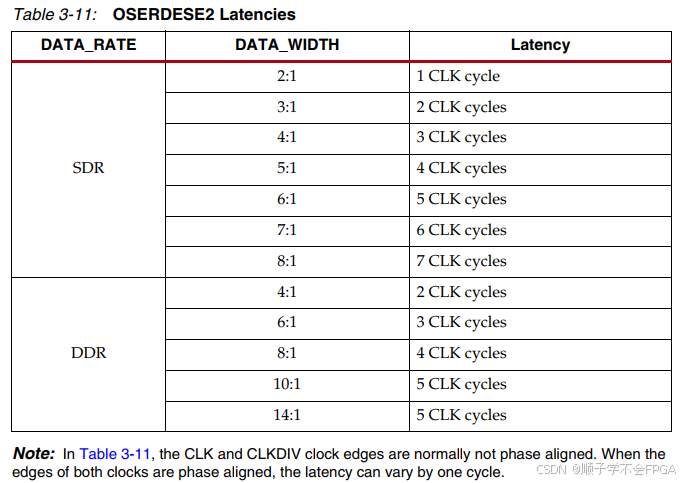

OSERDESE2块的输入到输出延迟指的是当CLKDIV的上升沿把输入数据D1~D8端口的数据寄存到OSERDESE2内部时 到 OSERDESE2的OQ端口输出第一位数据的时间间隔。当CLK和CLKDIV的相位对齐时,延迟可能相差一个CLK周期,如果CLK和CLKDIV的相位没有对齐时,延迟的值取决于DATA_RATE和DATA_WIDTH的值,如下图所示:

三、OSERDESE2时序

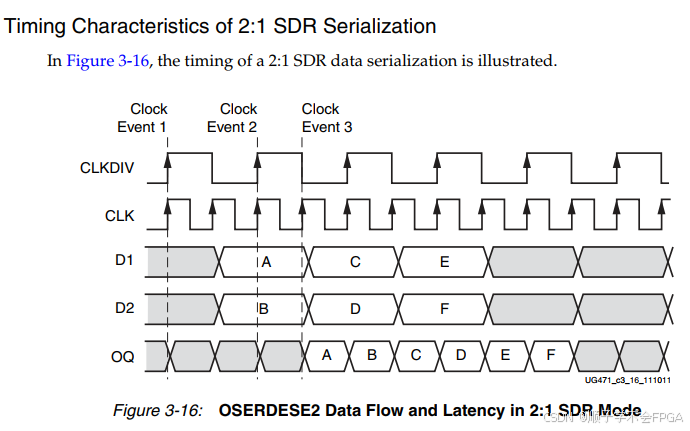

3.1、SDR模式

-

时钟事件1在CLKDIV的上升沿上,2’bAB从FPGA逻辑驱动到OSERDESE2的D1和D2输入(需要经过一些传播延迟)。

-

时钟事件2在CLKDIV的上升沿上,2’bAB从D1和D2输入采样到OSERDESE2。

-

时钟事件3数据位A在AB被采样到OSERDESE2后一个CLK周期出现在OQ。

-

此延迟与上表当中SDR模式OSERDESE2延迟为一个CLK周期一致。

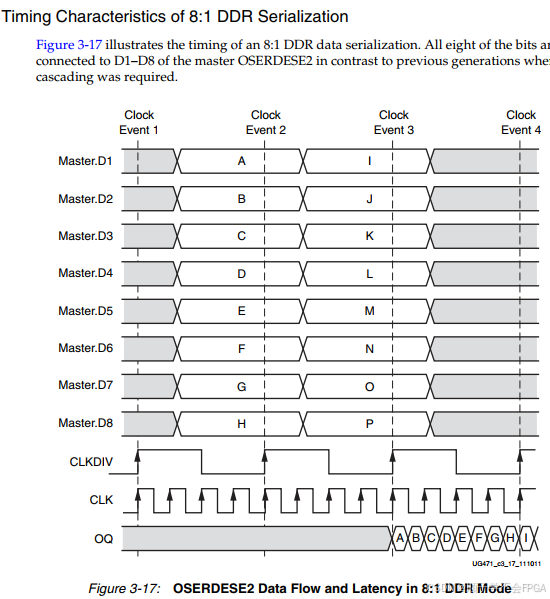

3.2、DDR模式

-

时钟事件1在CLKDIV的上升沿上,8’bABCDEFGH从FPGA逻辑驱动到OSERDESE2的D1-D8输入。

-

时钟事件2在CLKDIV的上升沿上,8’bABCDEFGH从D1-D8采样到OSERDESE2。

-

时钟事件3在ABCDEFGH被采样到OSERDESE2后,数据位A出现在4个CLK周期,与上表描述一致。第二个单词IJKLMNOP从D1-D8采样到OSERDESE2。

-

时钟事件4在时钟事件3和4之间,整个8’bABCDEFGH在OQ上串行传输,在一个CLKDIV周期中总共传输8位。在IJKLMNOP被采样到OSERDESE2之后,数据位I出现在OQ的四个CLK周期。

-

这个延迟与之前时延表中列出的4个CLK周期的8:1 DDR mode下OSERDESE2延迟一致。

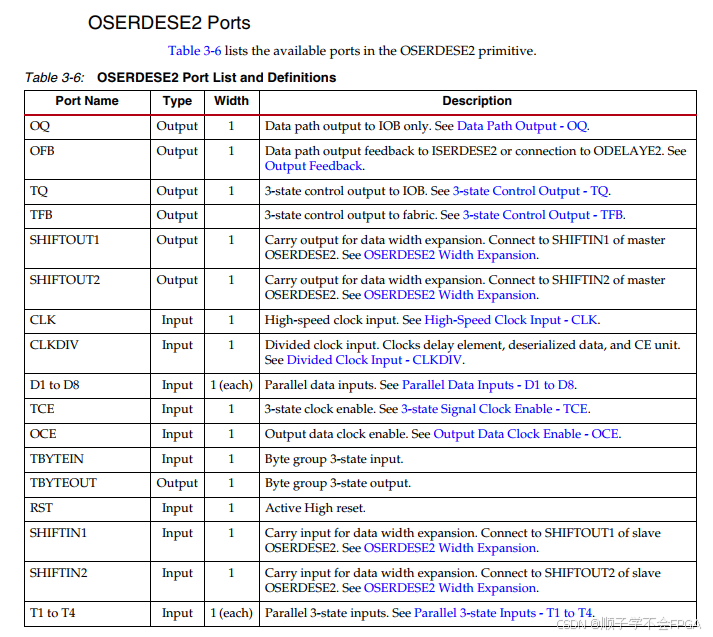

3.3、DDR模式下三态传输

此时最多将4位并行数据转为串行数据输出,在时钟CLKDIV第三个上升沿处,采集到D1-D4的数据位EFGH,与此时T1-T4的数据0010对应。

经过一个CLK时钟周期后,OQ输出第一个串行数据E,而TQ开始输出对应三态数据0,当TQ数据为0时,才会将OQ的数据输出到IOB模块,当TQ为1时,FPGA管脚作为输入,此时不会把OQ的数据输出到IOB。因此下图中当TQ为低电平时,OBUFT.O才输出OQ对应的数据EFH,否则不输出OQ的数据。图片