FPGA静态时序分析与约束(三)、读懂vivado时序报告

系列文章目录

FPGA静态时序分析与约束(一)、理解亚稳态

FPGA静态时序分析与约束(二)、时序分析

文章目录

- 系列文章目录

- 前言

- 一、时序分析回顾

- 二、打开vivado任意工程

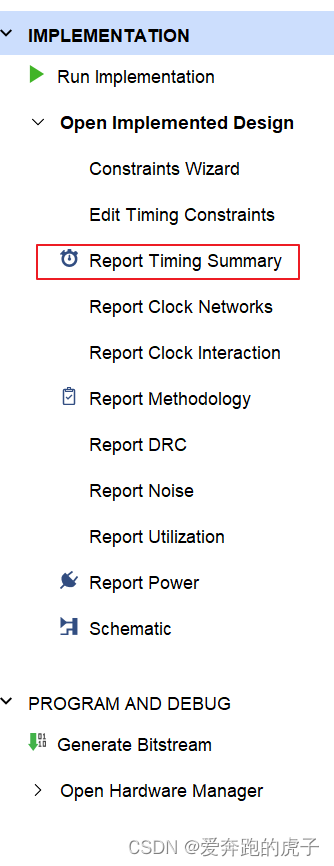

- 2.1 工程布局路由成功后,点击vivado左侧**IMPLEMENTATION**->再点击**Report Timing Summary**

- 2.2 在弹出的界面下面的命令栏,点击**Timing**

- 2.3 点击方框1里面的intra-Clock Paths

- 三、分析静态时序路径

- 3.1 分析源时钟路径

- 3.2 分析数据路径

- 3.3 分析目的时钟路径

- 四、 计算建立时间余量

前言

前两篇文章介绍了什么是亚稳态?以及静态时序分析,但那些终究还是理论,那么在实际工程中,如何分析时序路径呢?如何将理论转到实际呢?

一、时序分析回顾

上篇文章我们知道了建立时间余量和保持时间余量公式为:

- 数据到达时间 Data Arrival time = Tclk1 + Tco + Tdata

- 数据锁存时间 Data Required Time = 锁存沿时间 + Tclk2 - Tsu

- 建立余量公式Setup Slack= 数据锁存时间 - 数据抵达时间

- 数据保持时间 Data Hold Time = Tclk1 + Tco + Tdata +时钟周期

- 数据锁存时间 Data Required Time = 锁存沿 + Tclk2 + Th

- 保持余量 = 数据保持时间 - 数据锁存时间

二、打开vivado任意工程

平台:vivado2020.1

2.1 工程布局路由成功后,点击vivado左侧IMPLEMENTATION->再点击Report Timing Summary

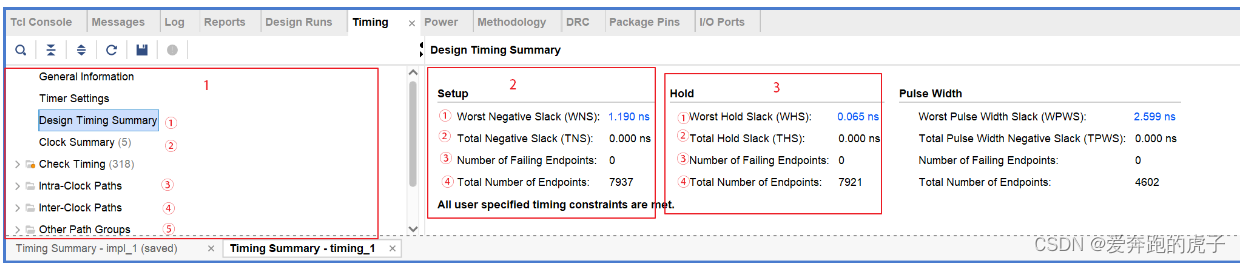

2.2 在弹出的界面下面的命令栏,点击Timing

- 方框1里:

①:整个设计的时序总结,如右边两个方框所示

②:整个设计里所有使用的时钟

③:相同时钟域路径

④:异步时钟域路径 - 方框2显示的是建立时间总共的信息:

①:最差建立时间余量

②:总的负建立时间余量之和

③:建立时间违规的节点路径数量

④:总的节点建立时间路径数量 - 方框3显示的是保持时间总共的信息:

①:最差的保持时间余量

②:总的负保持时间余量之和

③:保持时间违规的节点路径数量

④:总的节点保持时间路径数量

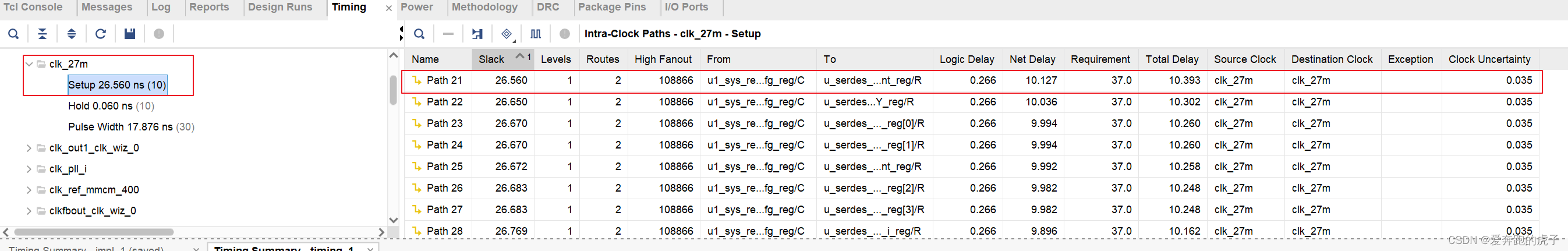

2.3 点击方框1里面的intra-Clock Paths

随便点击一个时钟域,看右侧的路径

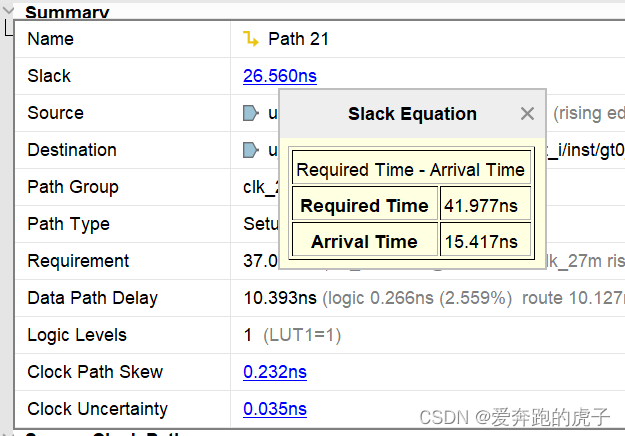

右侧会显示最差的时序的路径(默认十条),双击path21

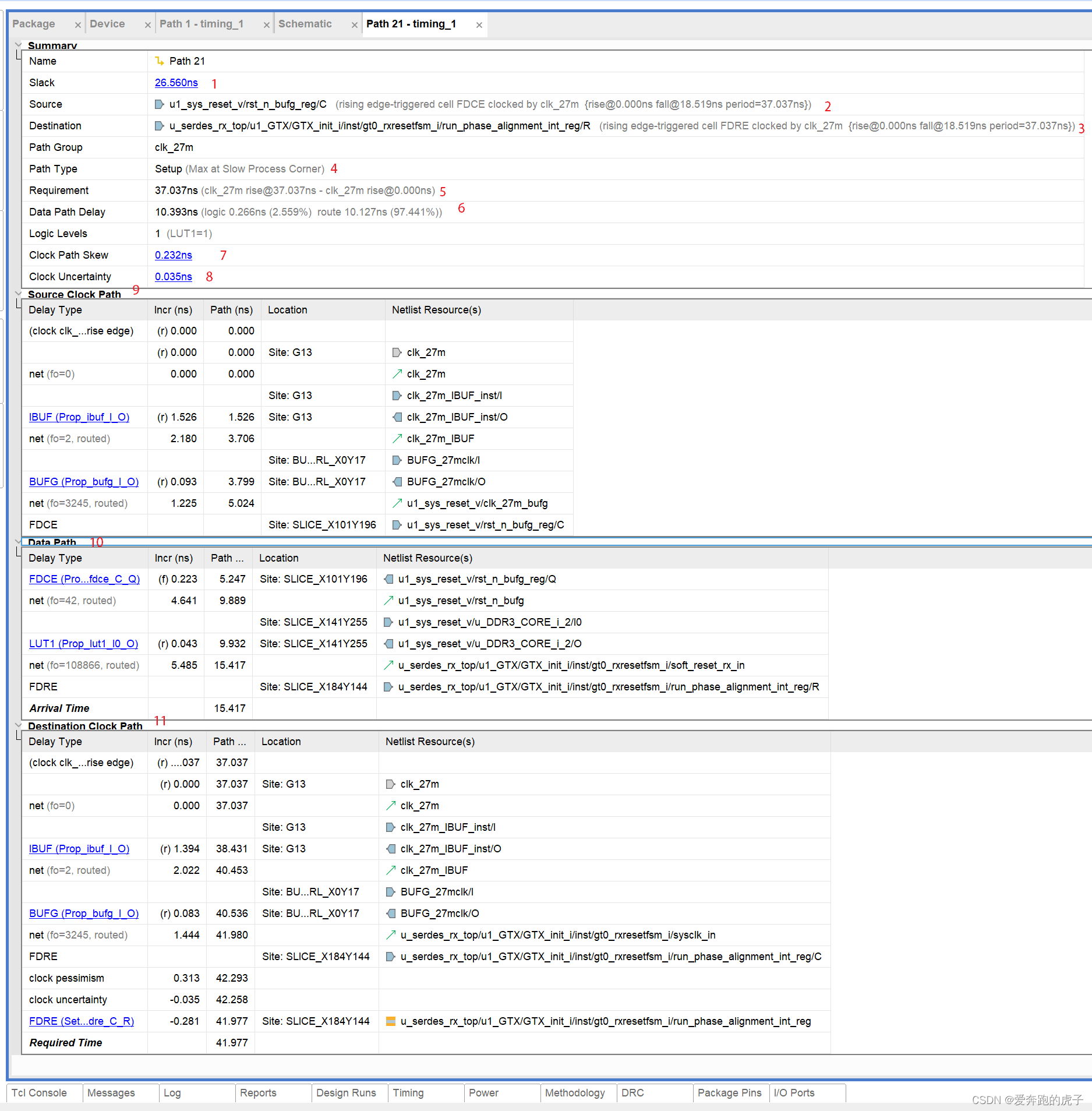

- 为该路径的时序余量,等于Data Required Time - Data Arrival time

- 该路径源时钟,这里是27M,周期37.037ns

- 该路径目的时钟,因为这里是同时钟域下的节点路径,所以也是27M,周期37.037ns

- 时序模型为建立时间

- 理想的建立时间为一个周期,参考FPGA静态时序分析与约束(二)、时序分析

- 这条路径总的数据延迟时间,Tdata

- 时钟偏斜

- 时钟的不确定性

- 源时钟路径

- 数据路径

- 目的时钟路径

三、分析静态时序路径

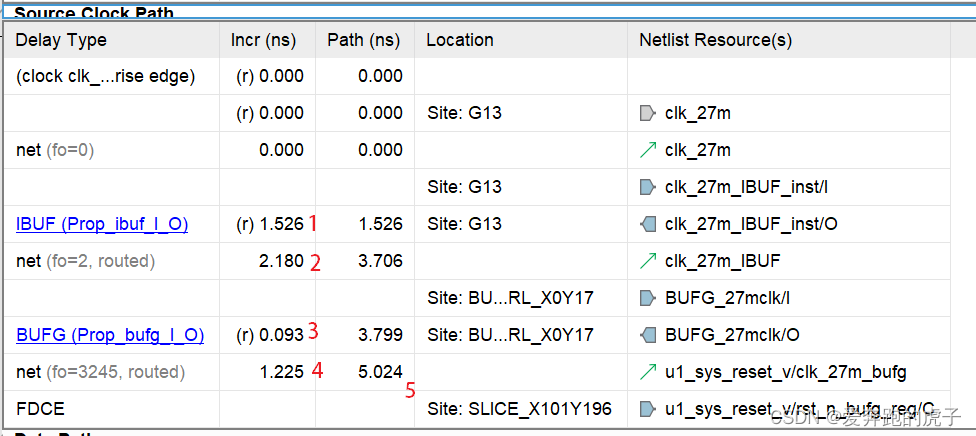

3.1 分析源时钟路径

- 时钟从外部管脚进来,经过IBUF,延迟了1.526ns

- 再经过走线net 延迟了2.18ns

- 然后进入BUFG延迟了0.093ns

- 最后经过走线net延迟了1.225ns,到达源寄存器时钟端口

- 总共源时钟路径Tclk1 = 1.526 + 2.18 + 0.093 + 1.225 = 5.024

3.2 分析数据路径

- 数据经过源寄存器Tco时间0.223ns

- 数据经过走线net延迟了4.641ns

- 数据再经过组合逻辑延迟了0.043ns

- 数据最后经过走线延迟了5.485ns

- 根据公式Data Arrival time = Tclk1 + Tco + Tdata=5.024 + 0.223 + (4.641 + 0.043 + 5.485)=15.417ns

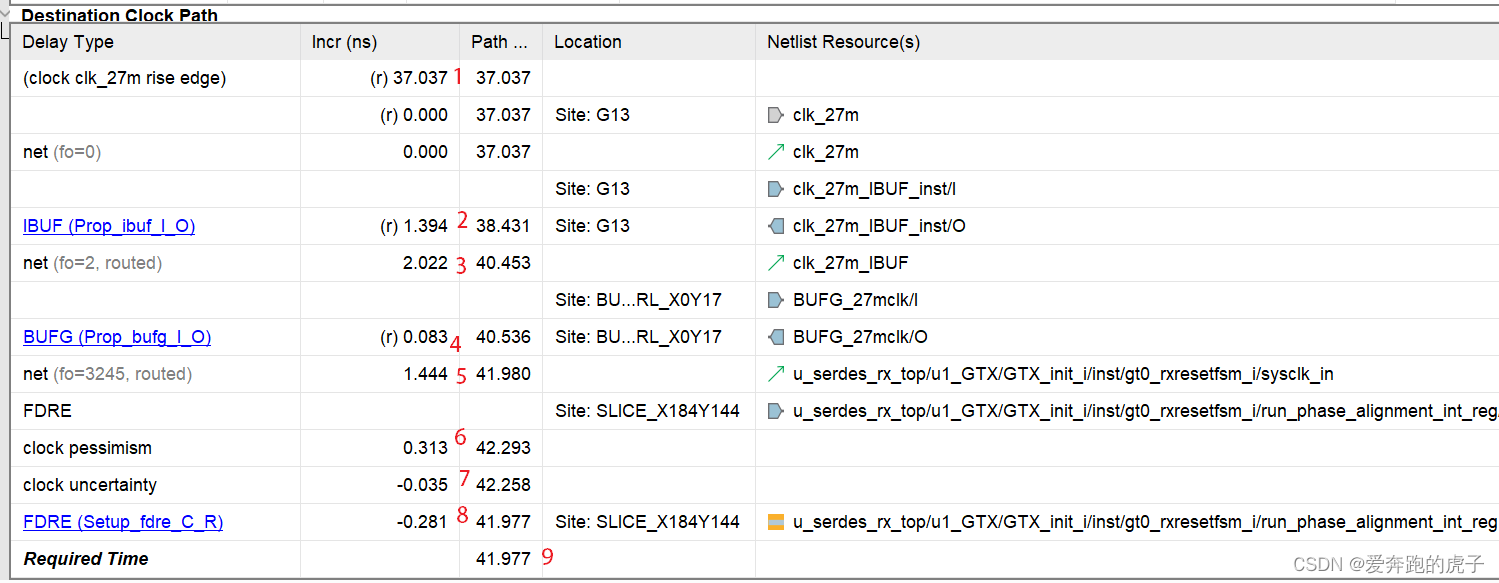

3.3 分析目的时钟路径

- 锁存沿时间,一个时钟周期37.037ns

- 进入IBUF延迟了1.394ns

- 经过走线延迟了2.022ns

- 经过BUFG延迟了0.083

- 走线延迟了1.444ns

- 时钟悲观延迟,由软件自动算出的延迟0.313ns

- 时钟不确定性因素,-0.035ns

- 寄存器建立时间0.281ns

- Data Required Time = 锁存沿时间 + Tclk2 - Tsu=37.037 + (1.394+2.022+0.083+1.444+0.313 -0.035)-0.281=41.977ns

四、 计算建立时间余量

根据建立余量公式Setup Slack= 数据锁存时间 - 数据抵达时间=41.977-15.417=26.560ns

和显示时间余量的一样。

以上就是对viavdo建立时间余量报告的解读,保持时间同理。

FPGA静态时序分析与约束(四)、时序约束