FPGA DDR3简介及时序

一,DDR3基础知识

1、DDR3全称第三代双倍速率同步动态随机存储器。

特点:①掉电无法保存数据,需要周期性的刷新。

②时钟上升沿和下降沿都会传输数据。

③突发传输,突发长度Burst Length一般为8

2、DDR3的存储: bank、行地址和列地址

数据怎么存入到DDR3:先指定一个Bank地址,再指定行地址,最后指定列地址。

DDR3容量计算: bank数量×行数量×列数量×存储单元容量。

比如bank address位宽为3, Row address位宽为14, Column address为10,

则容量为: 243 × 2^14 × 2^12 × 16bit

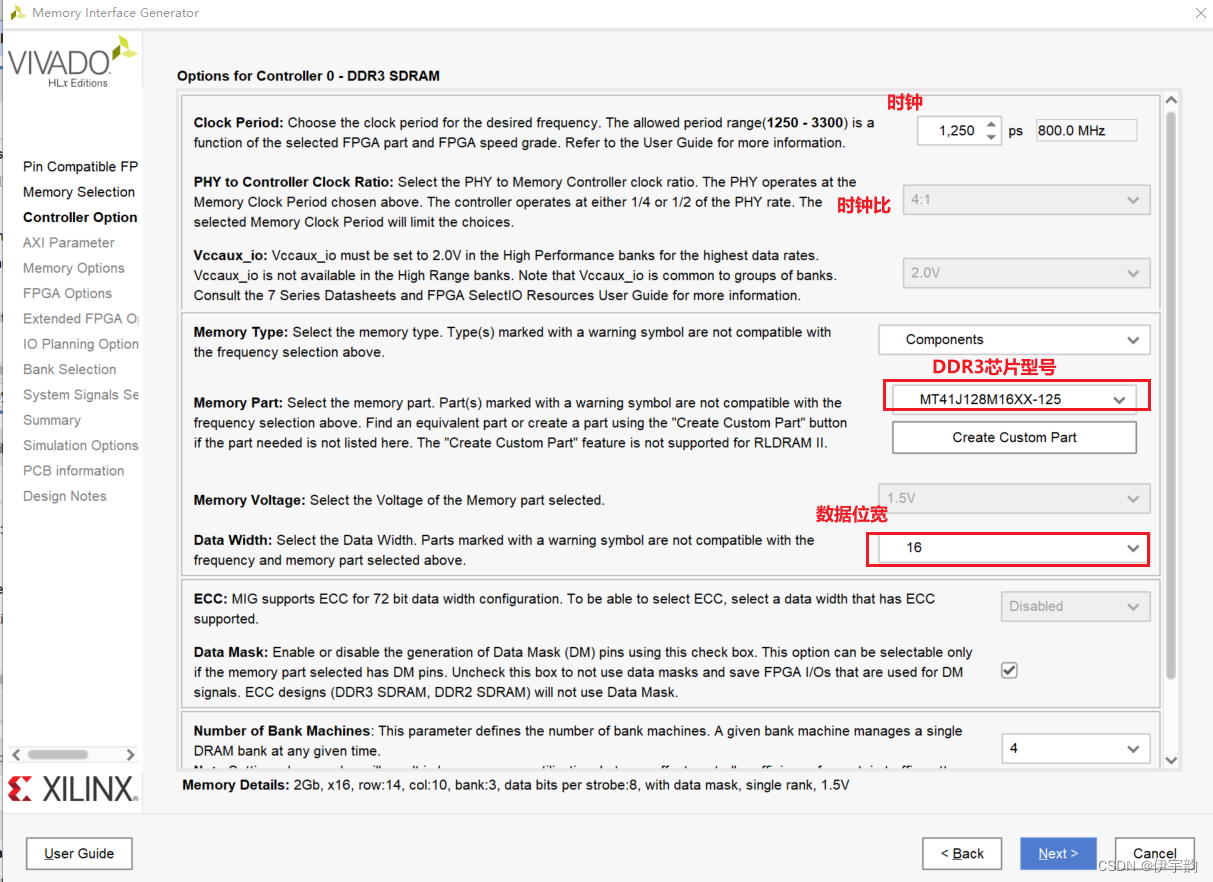

3,DDR3命名

以MT41K256M16 为例,其命名规则如下:

从DDR3的命名,我们可以得出几点有用的信息:

① DDR3 传输数据端口的位宽

② DDR3支持的最大的时钟频率

③ DDR3 传输数据的带宽

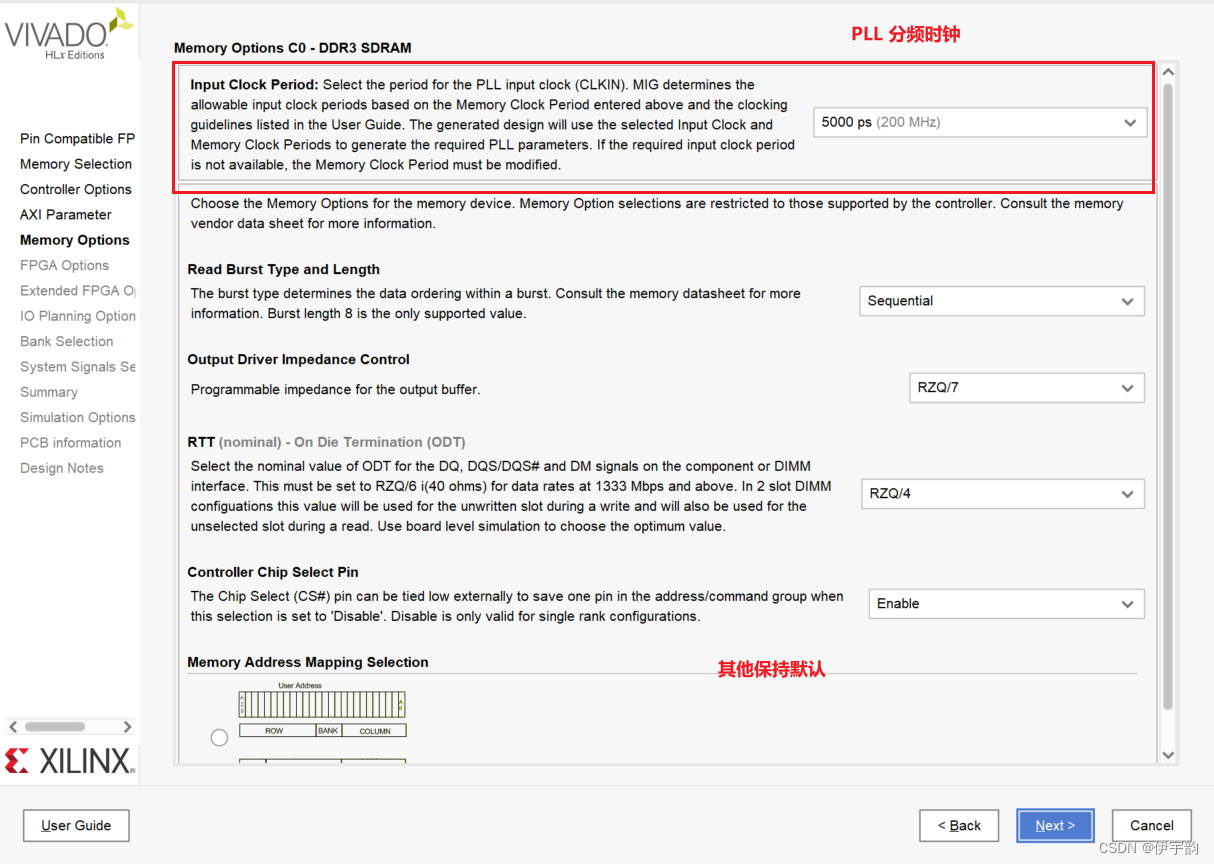

二,时钟

1、时钟类别(不要弄混淆哦)

系统时钟: MIG IP核工作时钟,一般命名为sys_clk。

参考时钟: MIG IP的参考时钟,必须为 200M,命名为ref_clk

DDR3芯片工作的时钟:由FPGA输入到DDR3芯片,为差分时钟

用户端时钟: MIGIP核输出给用户端的时钟,命名为ui_clk

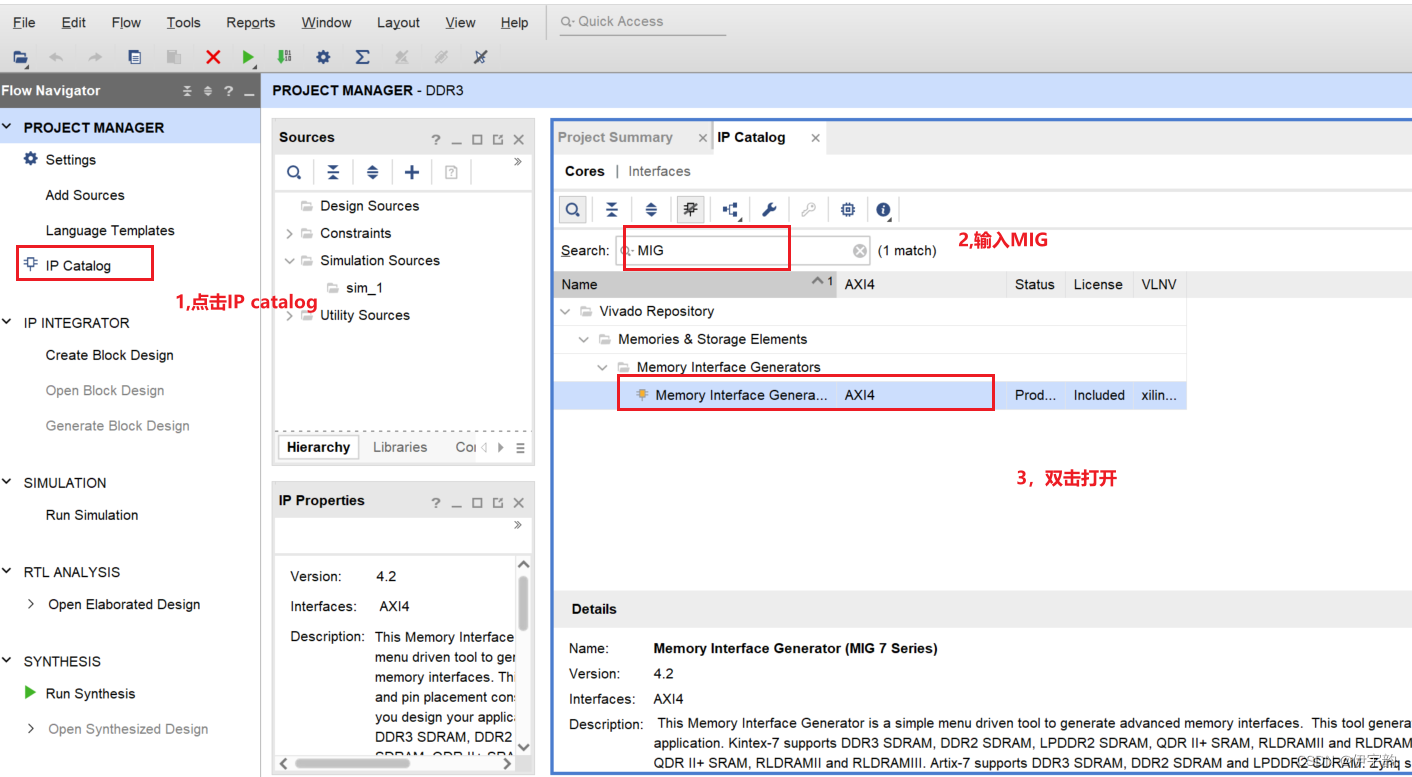

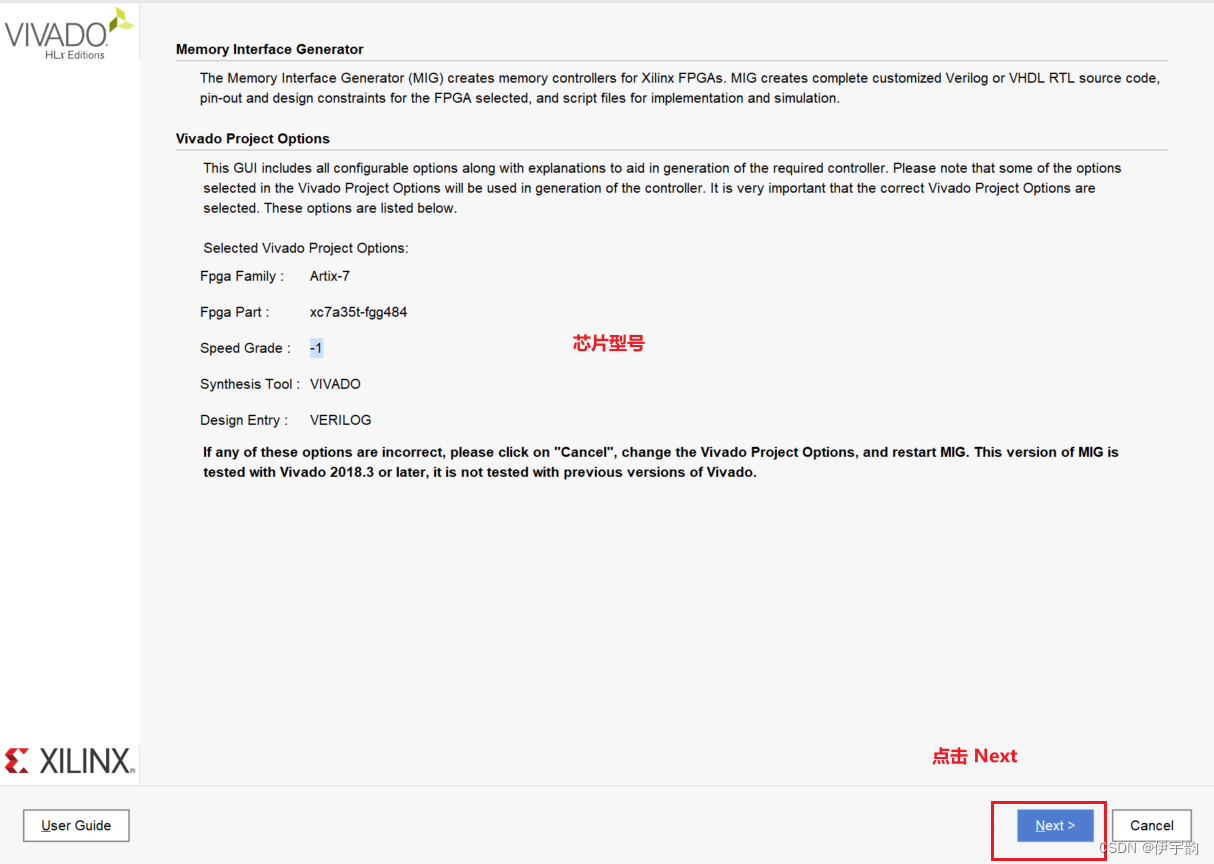

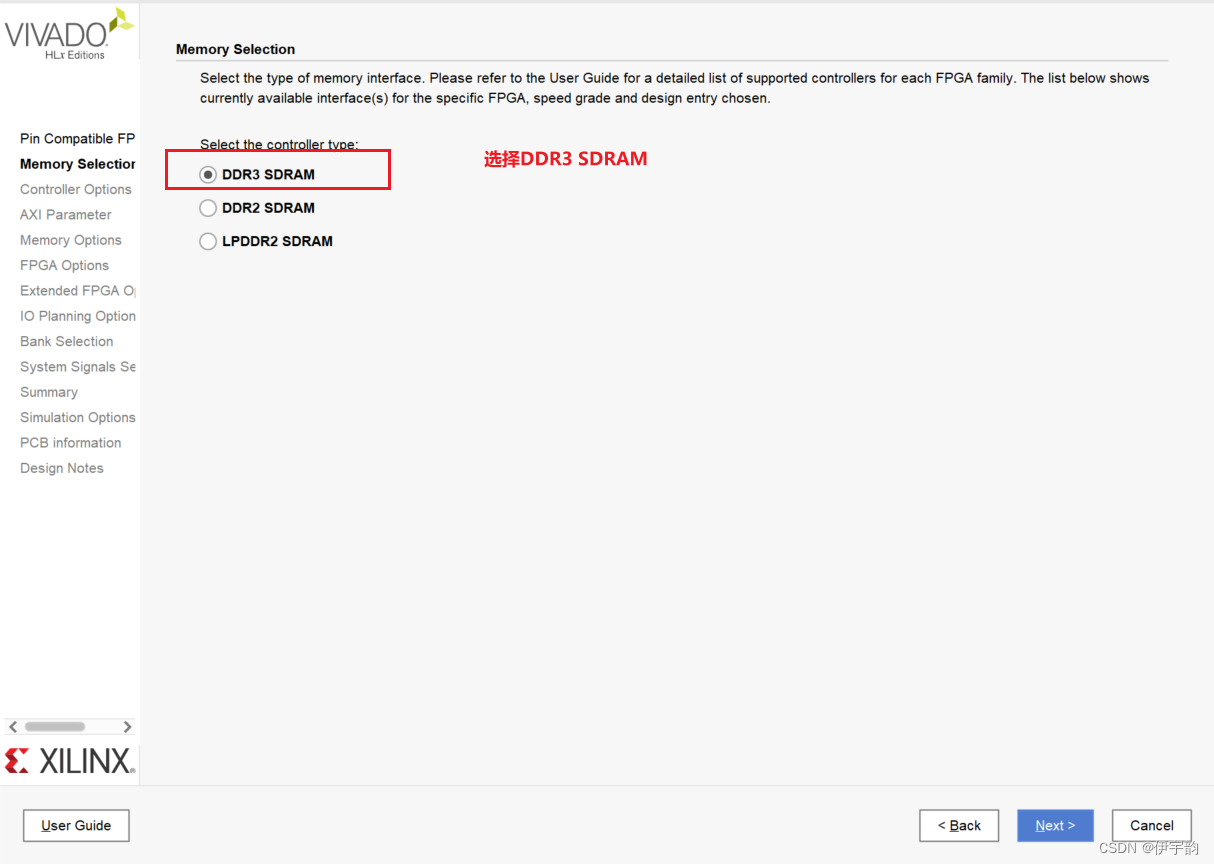

三,MIG IP核

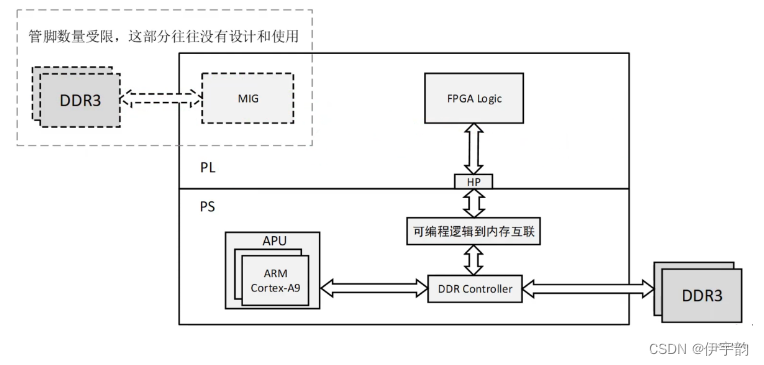

XILLNX FPGA芯片分为2种:

1,A7,X7系列(纯FPGA)

2,ZYNQ系列(带有ARM芯片)

这两种芯片往DDR3中写数据是不一样的

第一种直接用 MIG IP核 往里面写就可以了

第二种是不一样的 一般是挂载在PL端,往HP里面写数据(详情可参考FPGA-AXI4接口协议概述)

这里使用的是纯FPGA往DDR3写数据

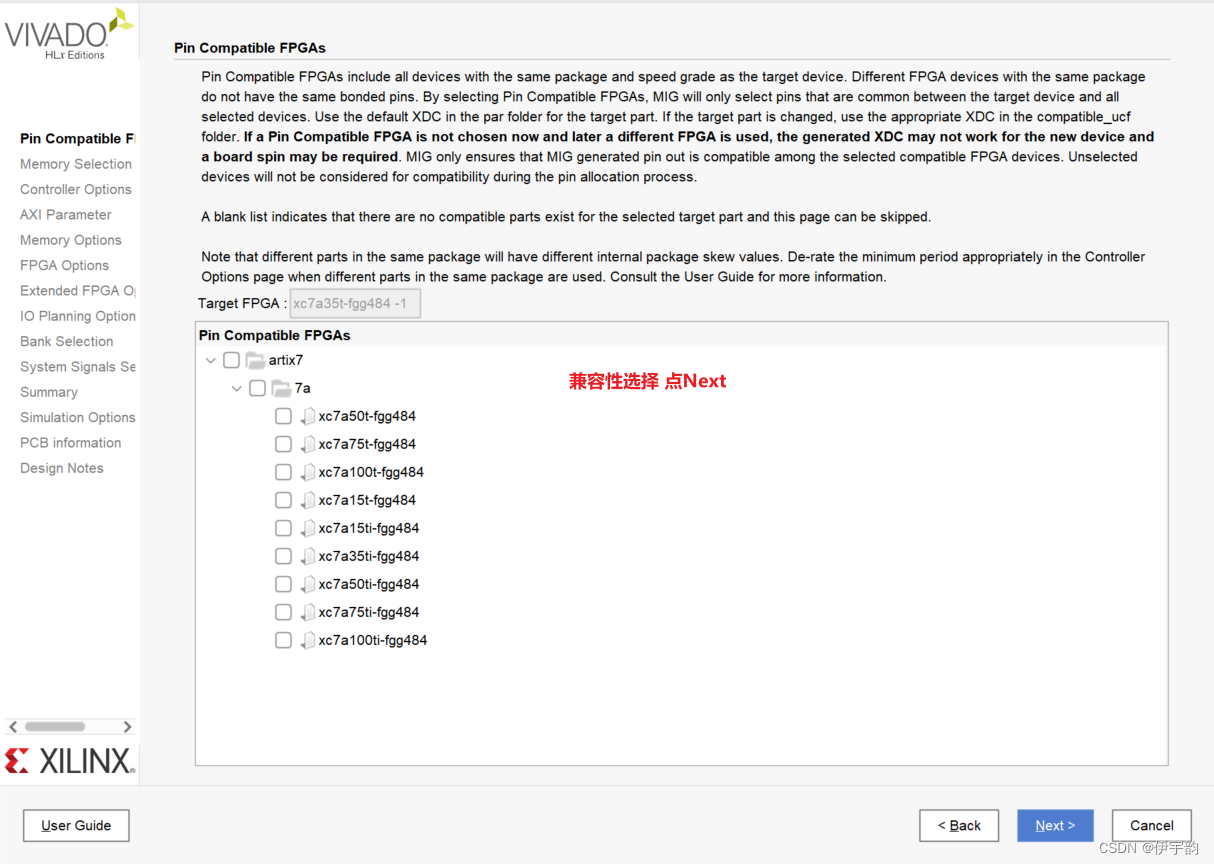

创建工程(参考FPGA_Vivado开发流程(PL端)3-8译码器为例)

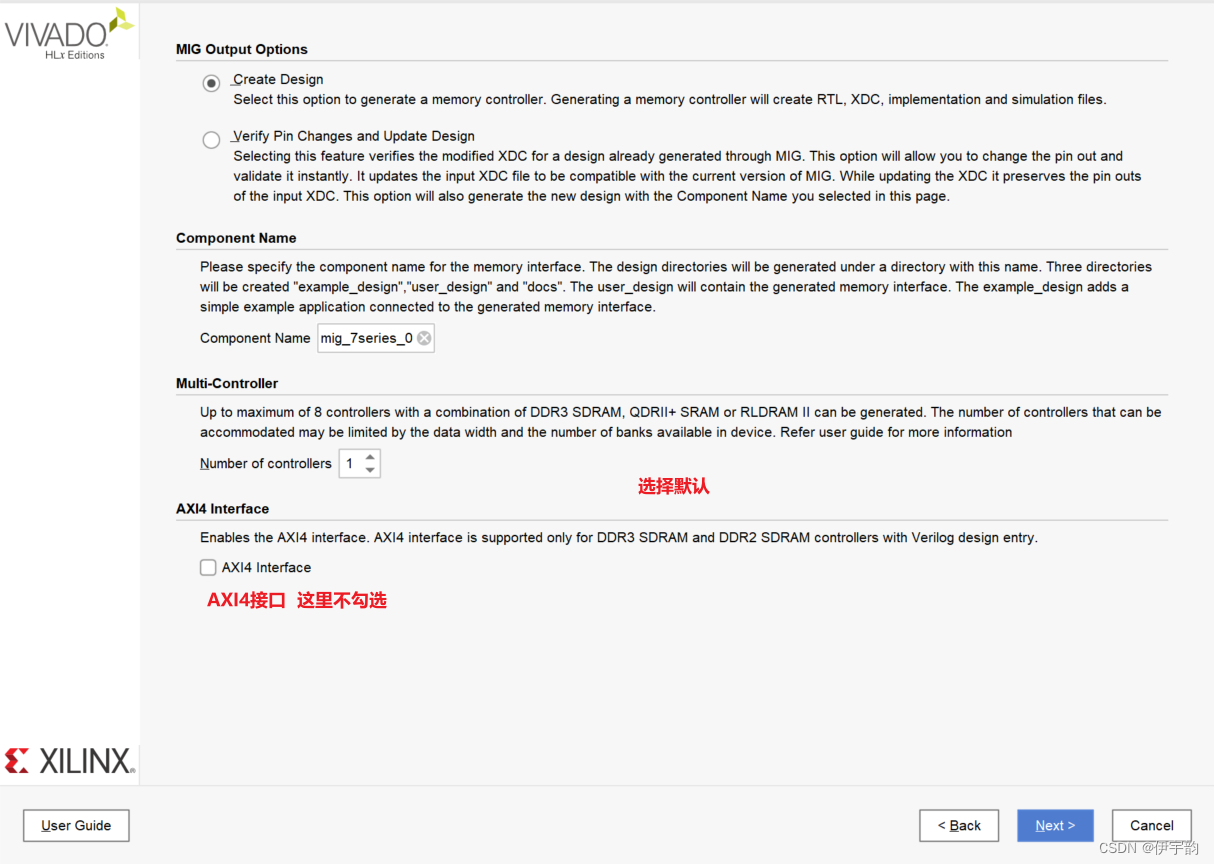

关于AXI4接口可查看这里

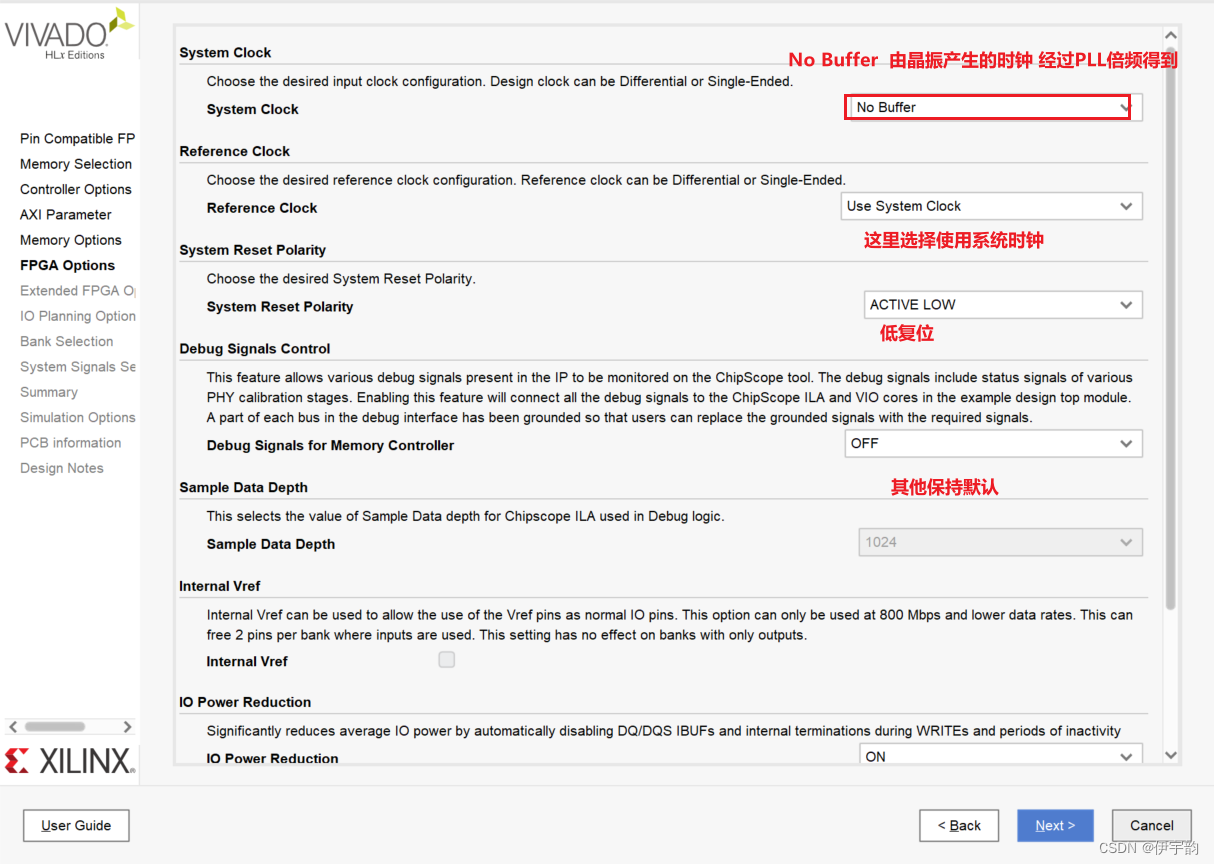

No Buffer 是什么意思?No Buffer 就是 MIG IP 核内部没有例化(IBUF 原语)

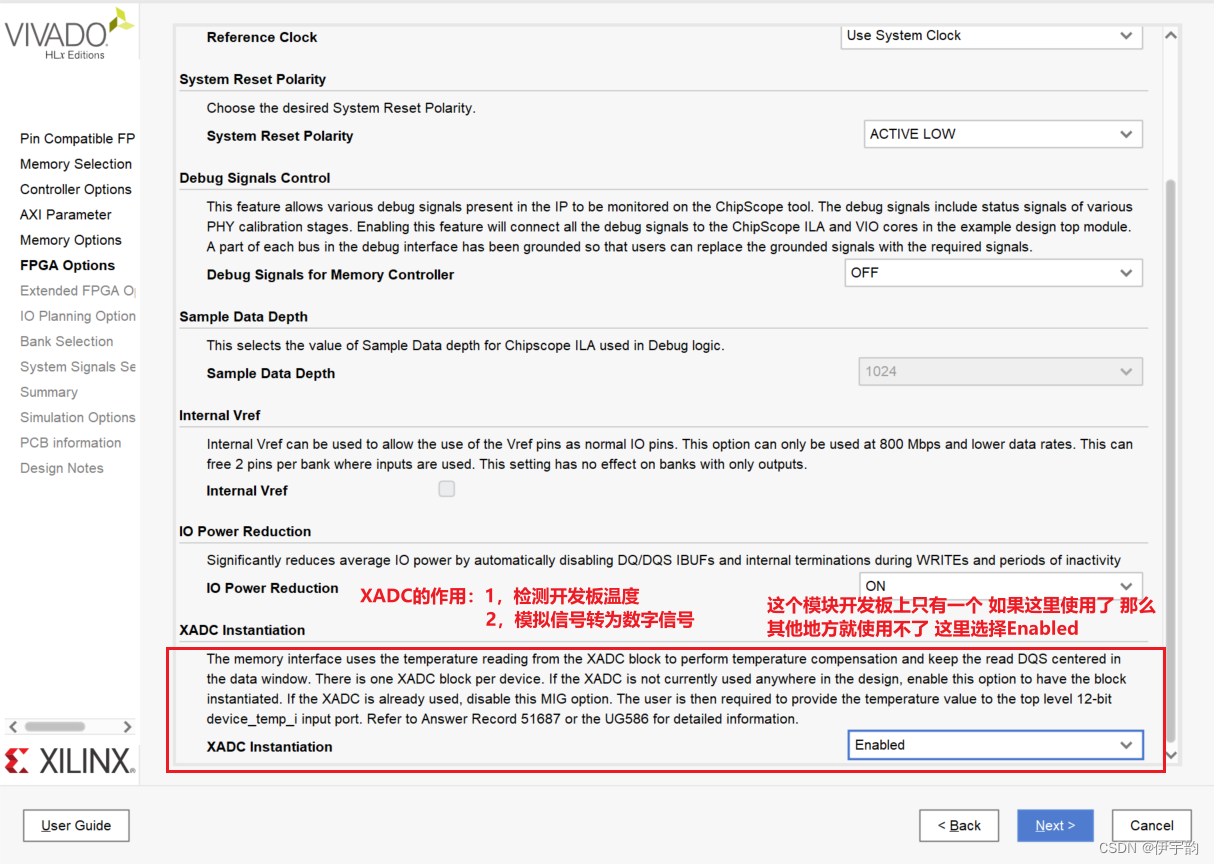

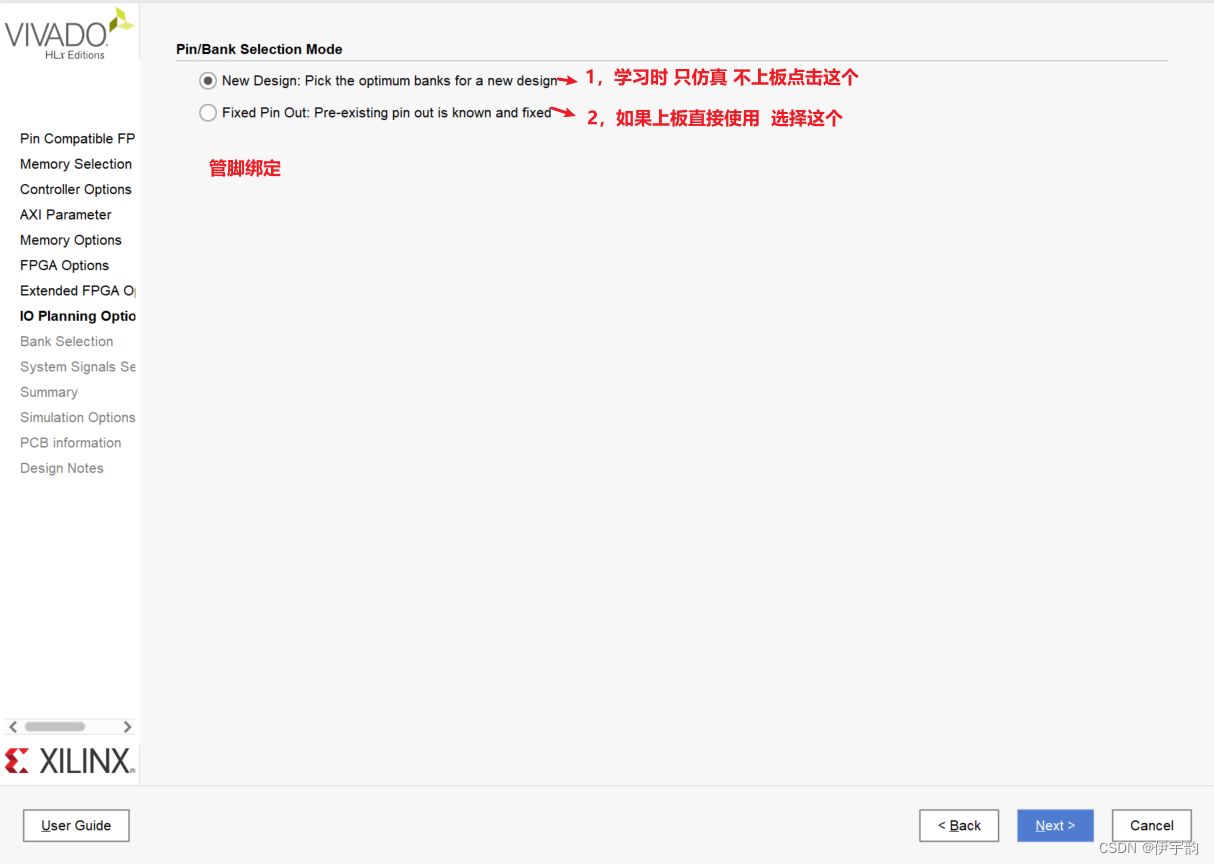

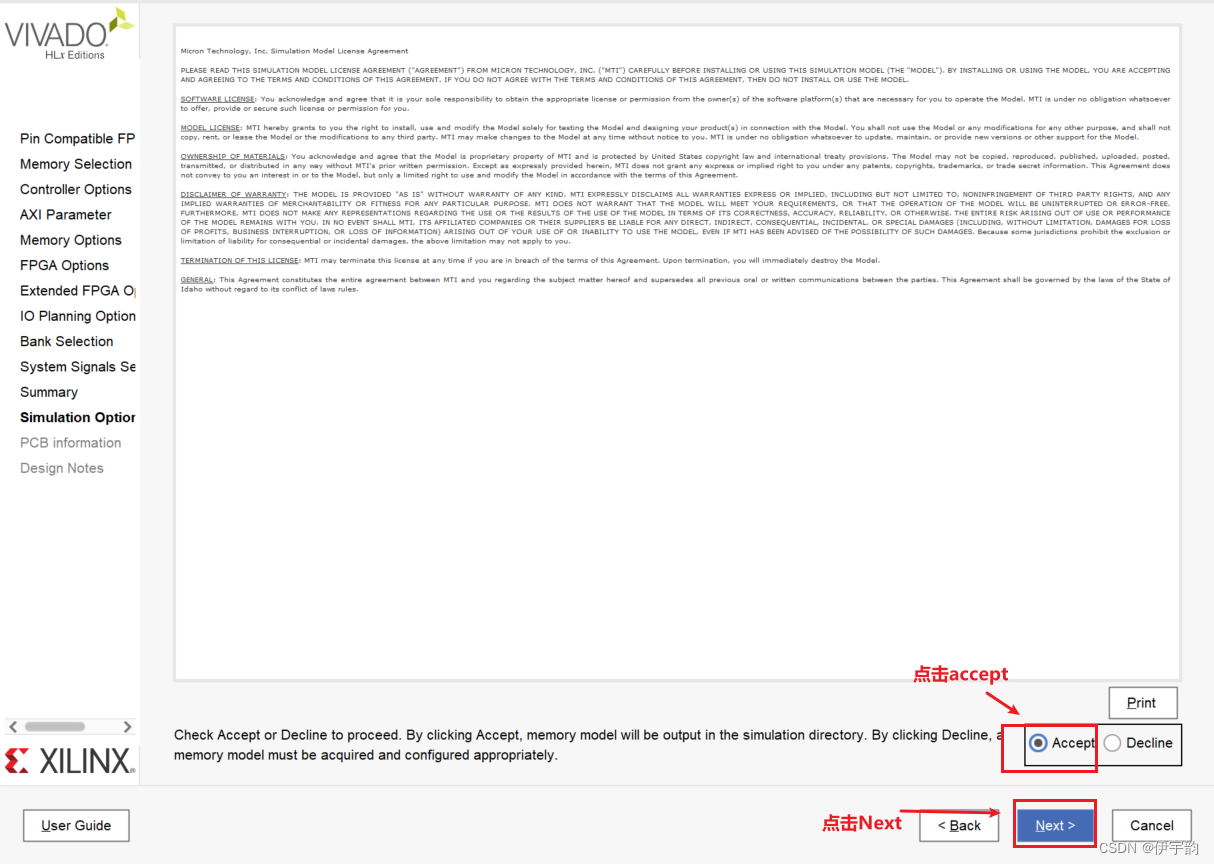

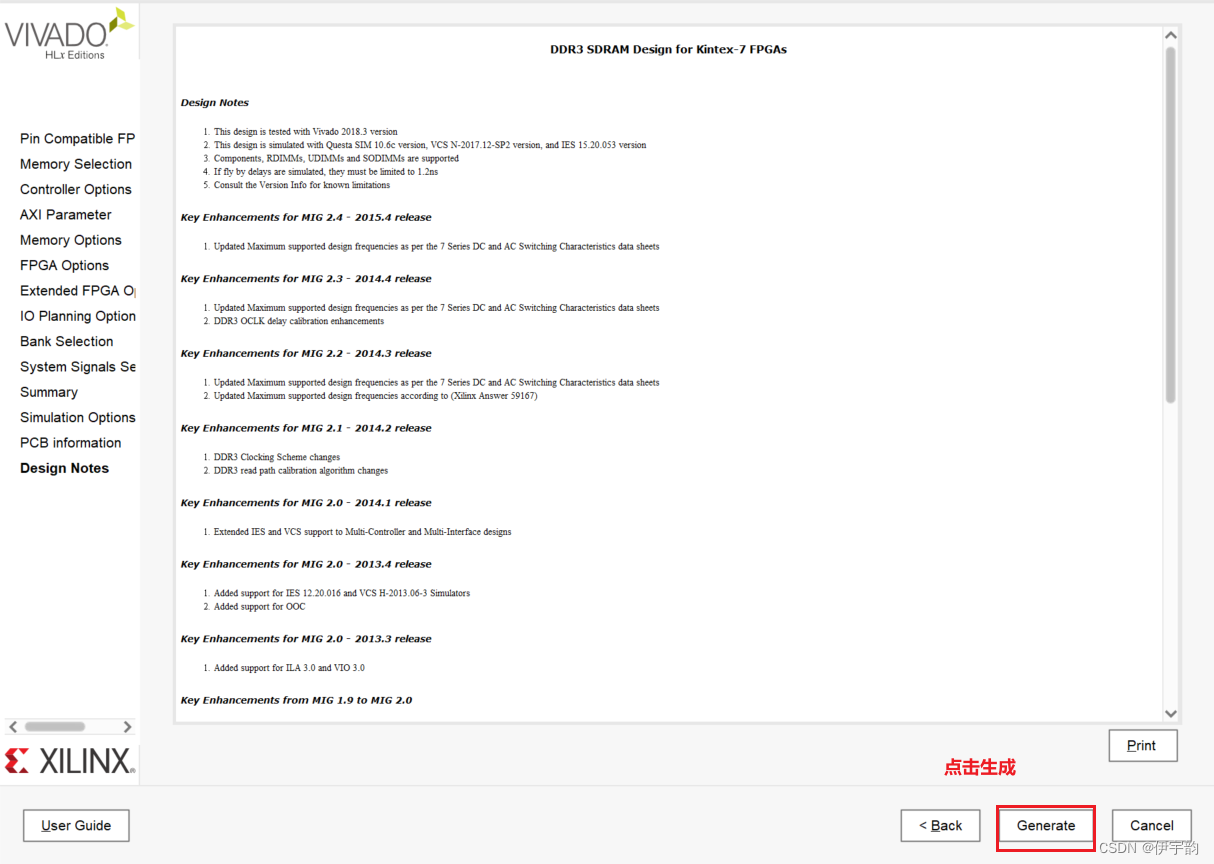

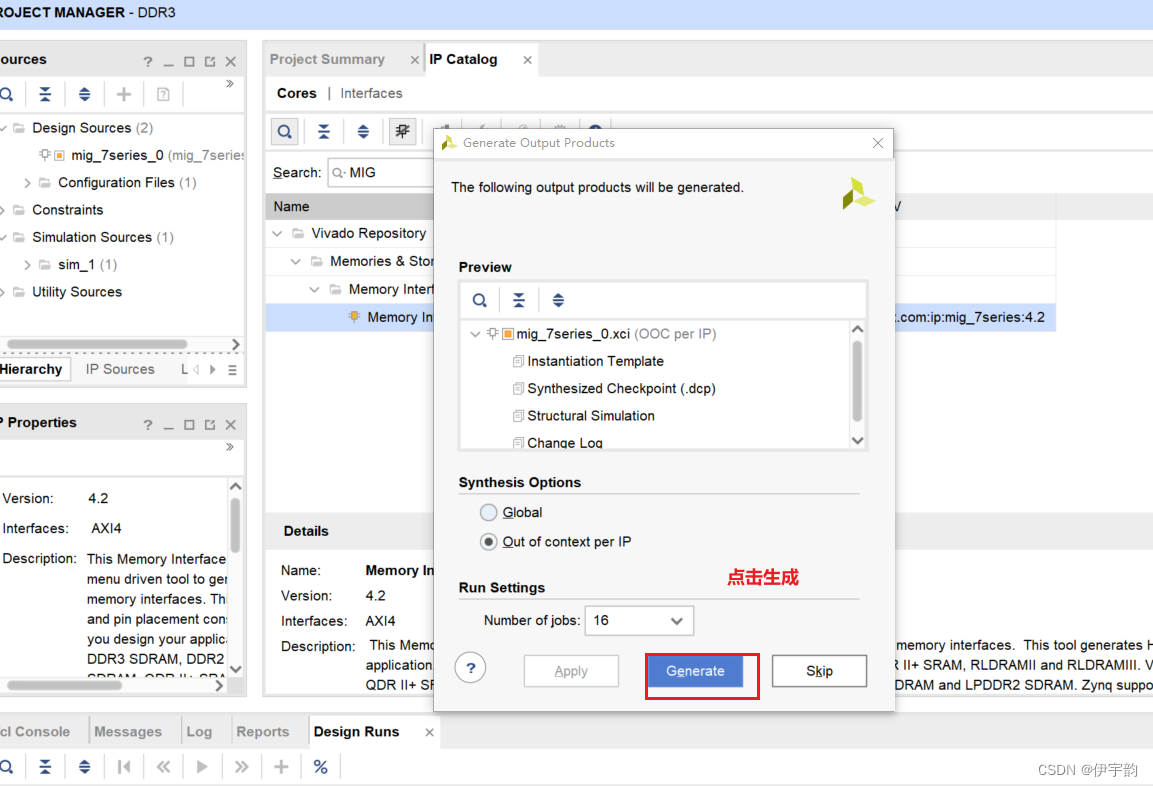

MIG IP 核配置结束

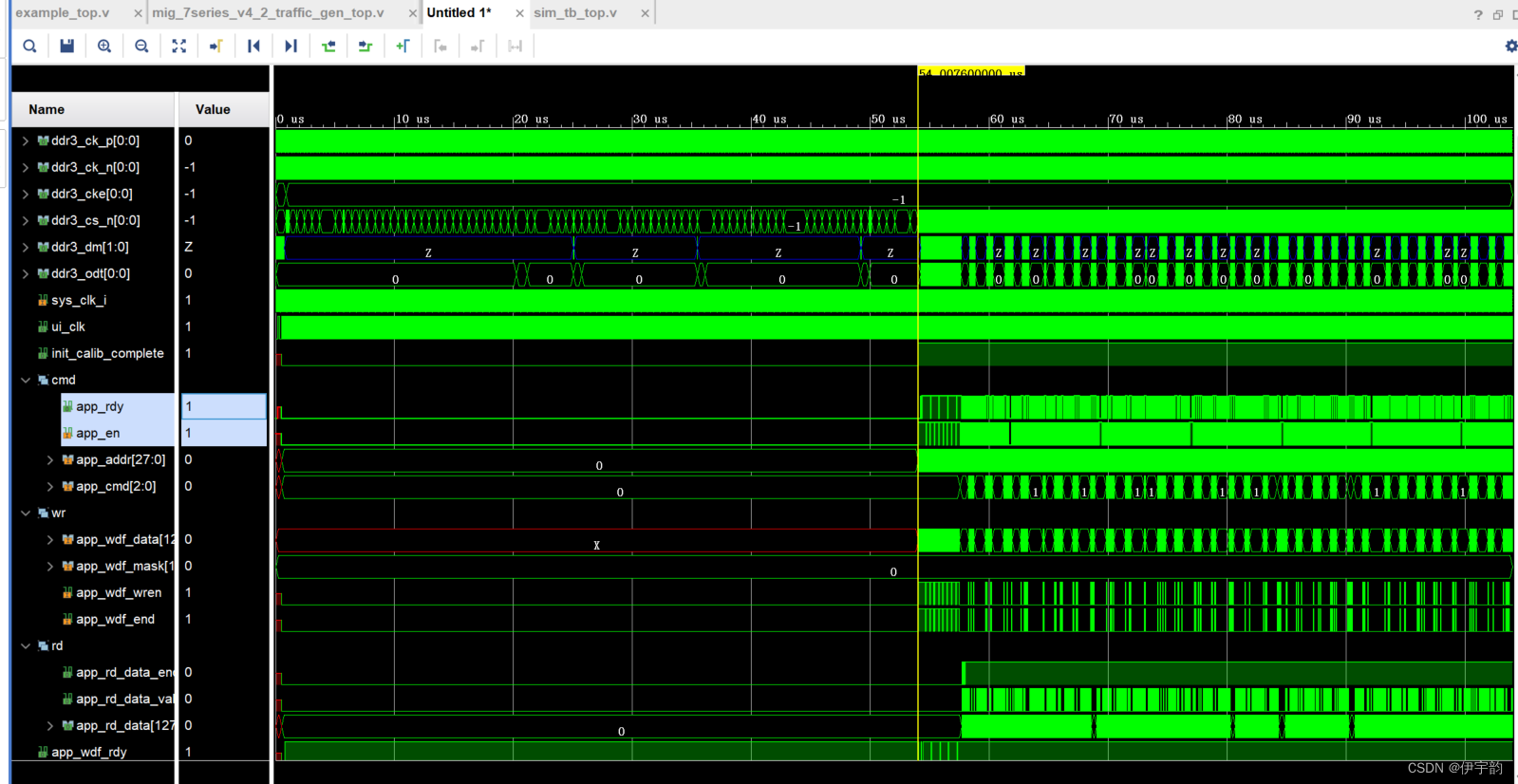

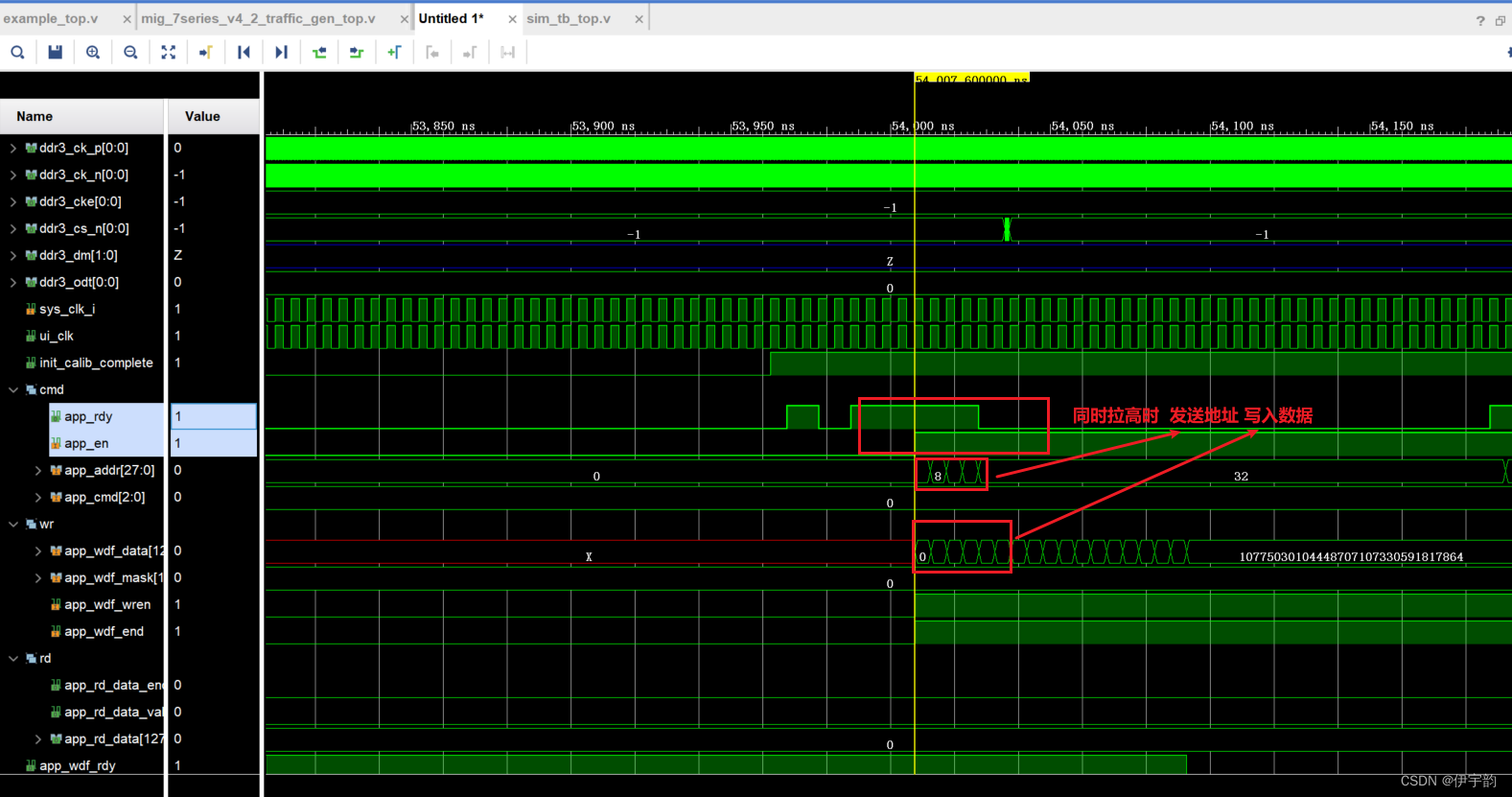

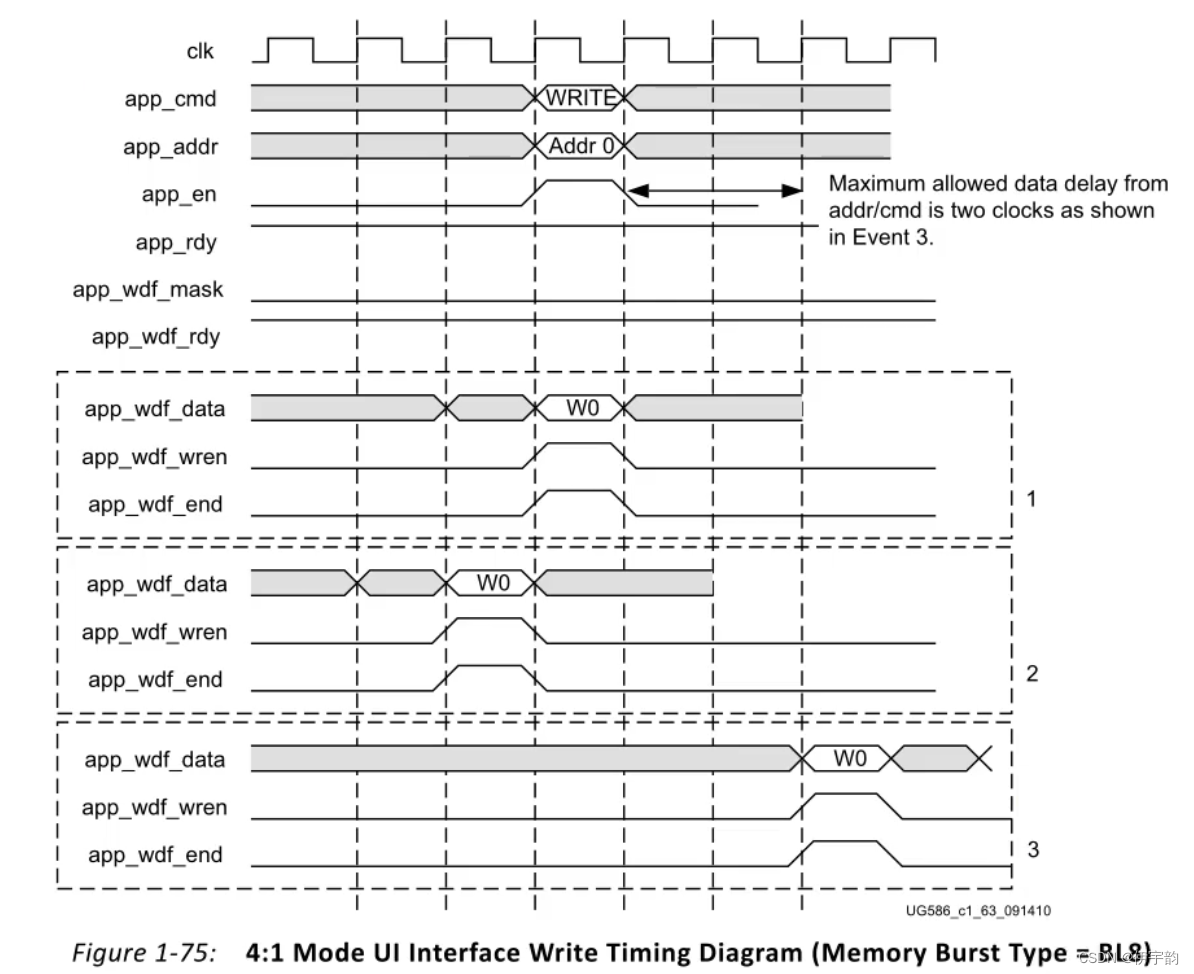

写数据时序图

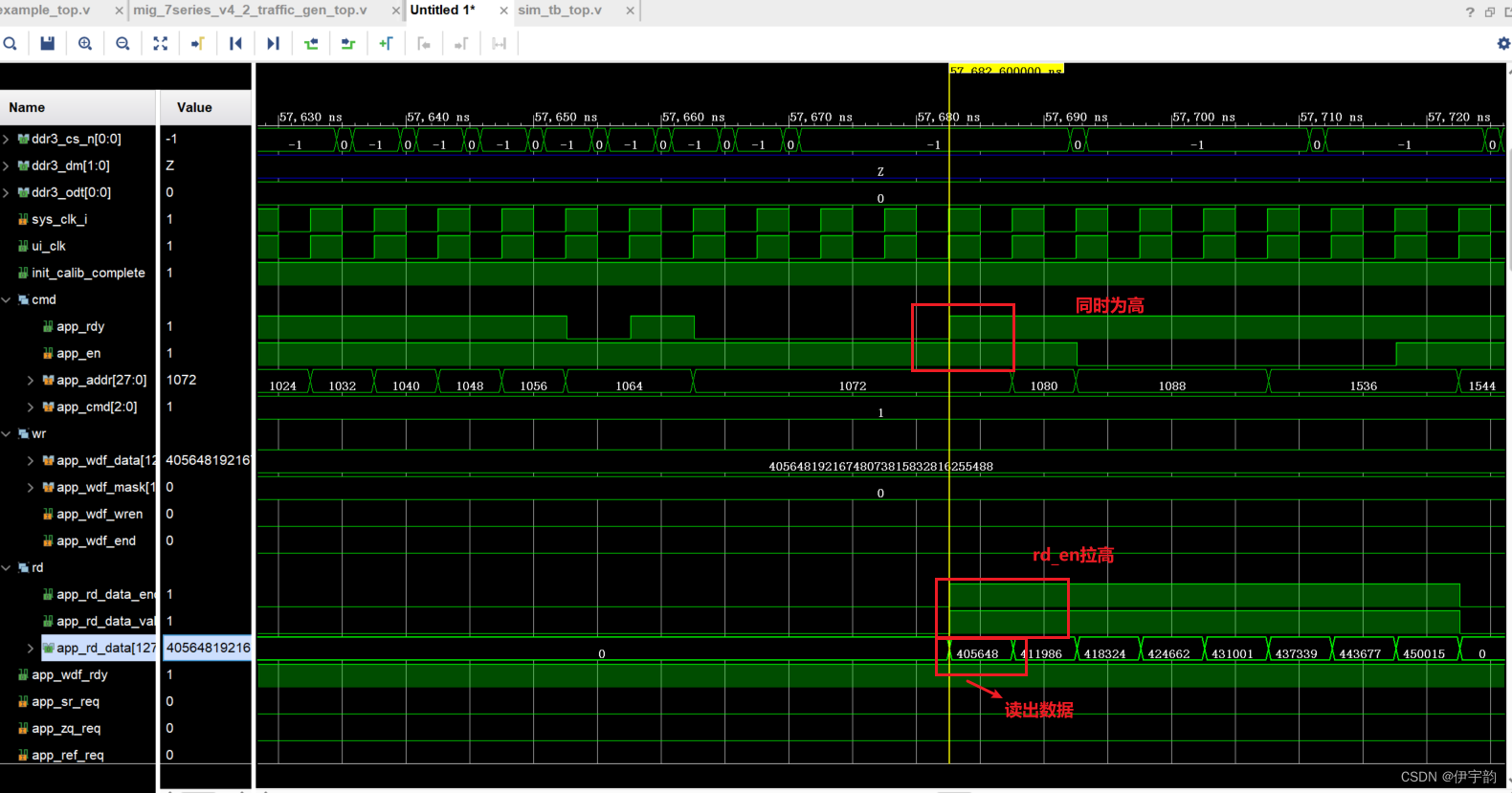

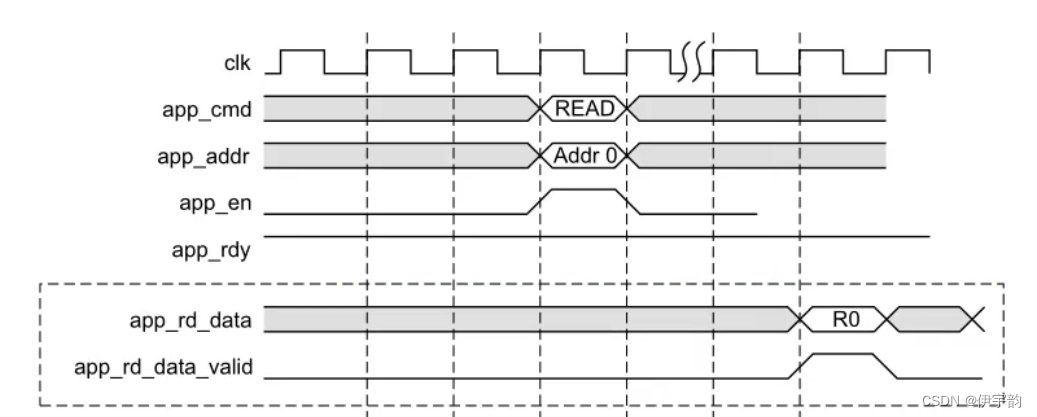

读数据时序图

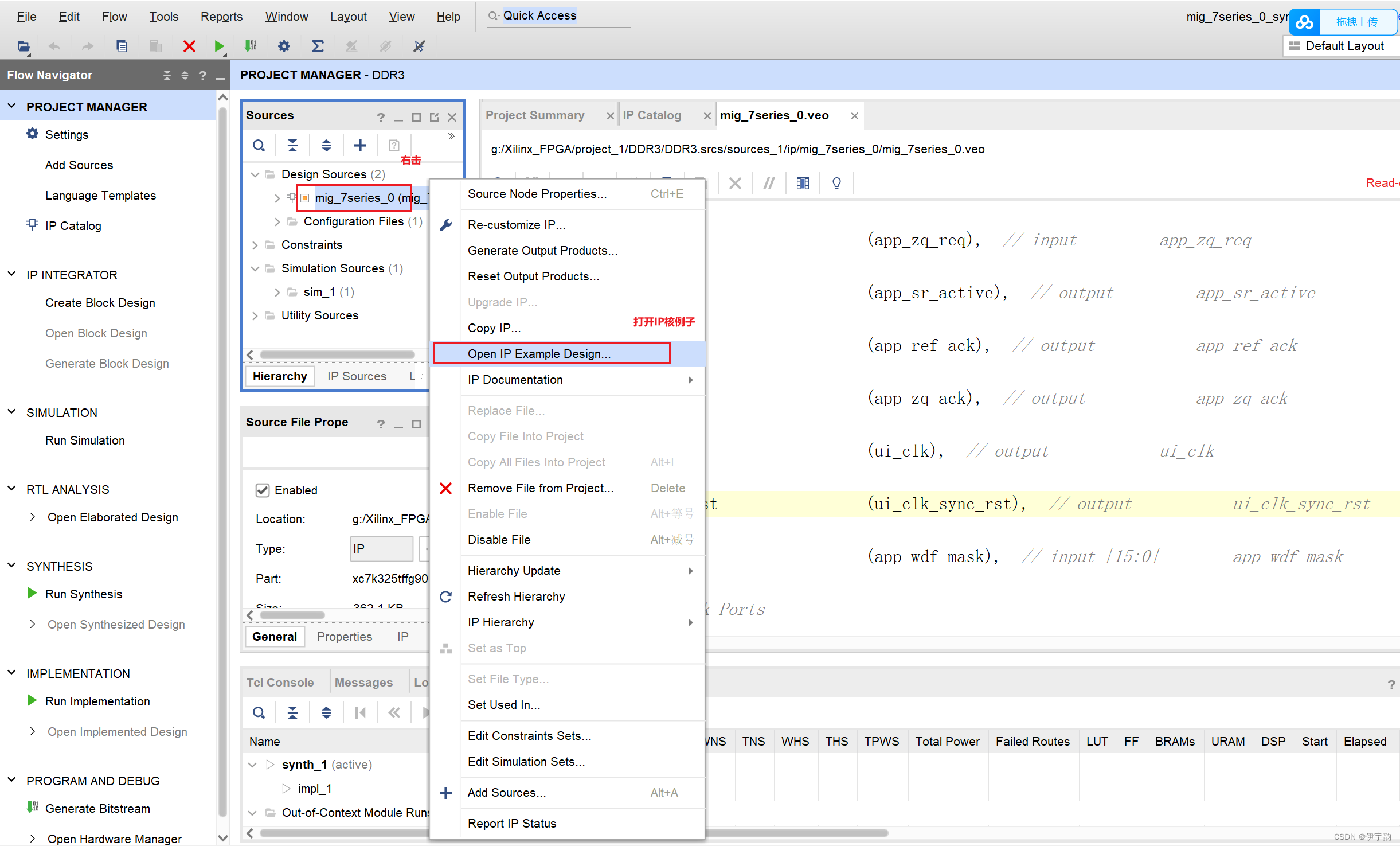

对打开的IP核例程 直接运行仿真

波形如下