PCIE 4.0 Equalizaiton(LTSSM 均衡流程)

1. 均衡

在Tx端有FFE(Feed Forward Equalizer,前馈均衡器);在Rx端有:CTLE(Continuous Time Linear Equalizer,连续时间线性均衡器)和DFE(Decision Feedback Equalizer,判决反馈均衡器)。通过FFE和CTLE,可以去除大部分由ISI所引入的抖动;通过DFE可以进一步去除ISI,它还能去除部分的阻抗失配所造成的反射。通过这些均衡处理,就能够最大程度上地保证在接收端判决输入处将眼图打开,保证信号的质量能够满足数据传输的要求。

再PCIE4.0版本之后,规范针对RC(downstream port) 以及EP (upstreamport)的phase分别进行了说明。

2. Downstream

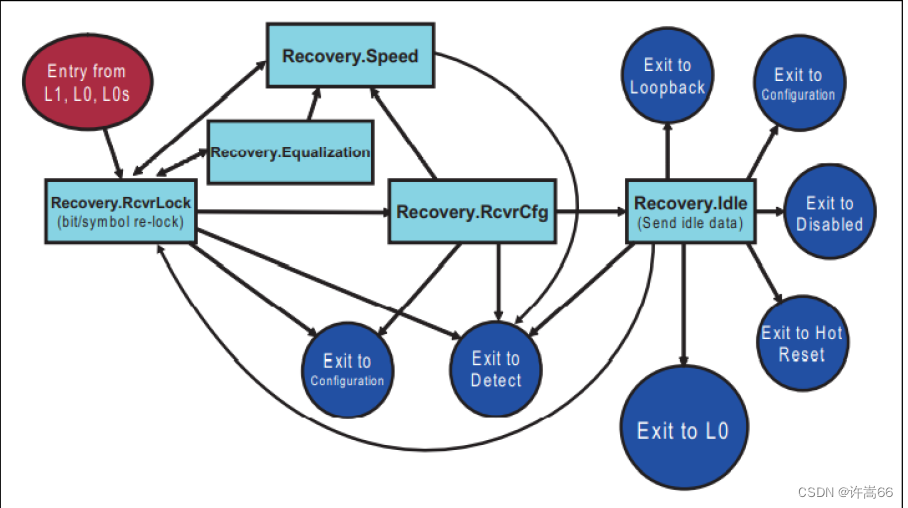

RC代表Downstream port, RC 需要从Recovery.rcvrlock 跳转到 Recovery.Equalization,它分为phase1 phase2 phase3 三个阶段。

2.1 phase1

在此阶段会清除当前速率(8GT or 16 GT)的EQ_phase_successfullz指示位,同时也会设置start_equalization_w_preset = 0 。在该子状态下RC会持续发送EC =01 (symbol6 ), Transmitter Preset 根据当前的速率分别进行设定, FS LT Cursor 这些系数则根据preset值进行设定的TS1 order set。

其中Transmitter Preset 设定遵循如下三种原则:(优先级依次降低)

1. 如果当前速度为16GT (Gen4) 则基于在Recovery.RcvrCf状态收到的8GT EQ TS2 order set中的Transmitter preset value进行设定。

2. 否则需要根据当前速率的Lane Equalization Control Register (8GT) or 16 GT/s Lane Equalization Control Register (16GT) 中的字 端进行设置。

3. 要用一种特殊实现的方法选择一个有效的Transmitter preset values。

note:如果RC需要调整自己Receiver 则允许在phase1 等待500ns后,再去评估接收到的TS1 order set。

phase1 -> phase2

所有configured lanes 收到两个连续的TS1 order set with EC=01,且 RC想去调整到下一个phase2 or phase3 (可以立即为RC自己对Receiver 调节自身的BER,以保证可以稳定接收后续的EQ order set)。 [必须保证在2ms内可以完成bit lock 并可以稳定识别 Order set;设置相应速率的phase1 successfull = 1 ]

phase1 -> Recovery.Rcvrlock

所有configured lanes收到两个连续的TS1 order set with EC=01,且 RC不想想去调整到下一个phase2 or phase3。 [设置相应速率的phase1/2/3 successfull = 1 complete bit = 1]

phase1 -> Recovery.Speed

上述两个条件未满足,24ms超时后调整。 [successful_speed_negotiation=0,当前speed的complete bit = 1]。

2.2 phase2

在该子状态TX会持续发送EC=10的TS1 order set,其关于FS LT cursor的系数设置在每条lanes是独立的,设置规则如下:

在接收到两个连续的EC=10的TS1 order set ,(包括当前的两次连续的TS序列中的参数,与上一次两次连续TS序列中的参数不同)的前提下,如果收到的preset 以及系数是合规的,则RC需要再收到第2个包含新请求的TS序列500ns内完成自身TX参数的调整(此时发送的TS1 序列中preset设置为请求的值,系数设置为Transmitter setting),否则保持当前TX电路的Transmitter setting 不变,但是需要在发送的TS序列中setting 设置为 EP请求的value并将Rejet Coefficient Vaule为1。

如果没有接收连续的的EC=10 的TS1 order set ,则按照当前的值保持不变。

phase2 -> phase3

所有configured lanes 收到两个连续的TS1 order set with EC=01,[必须保证在2ms内可以完成bit lock 并可以稳定识别 Order set;设置相应速率的phase2 successfull = 1]

phase2 -> Recovery.Speed

上述两个条件未满足,32~36ms超时后调整。 [successful_speed_negotiation=0,当前speed的complete bit = 1]。

2.3 phase3

在该子状态TX会持续发送EC=11的TS1 order set,会根据接收的TS1 order set评估信号质量,并向EP请求新的preset 和相关系数。若 Preset bit =1,此时是一个Preset 更改请求,否则是 Cursor 系数请求。另外协议要求RC必须持续请求1us,等待500+ns后,EP会使用RC请求的值填充子的TS1 序列的相应字段,并发送给RC。

只有RC接收到了从EP返回来的TS1 序列,且Preset以及相关系数相同,且Rejection Coefficient =0表示EP 接收了RC发送的请求。此外DSP负责发送的TS序列中设置Reset EIEOS Interval Count bit ,它根据自己的需求以及评估准测进行设定。

从请求到最终完成均衡一般不允许超过2ms,但是可以允许以同样的参数第二次尝试(此时的超时时间可以超过2ms但是不能超过24ms的状态超时),所有的lanes需要同时发送new preset and 系数,但是如果其中一些lane不需要改变当前设置,也是允许保持当前值不变继续发送。

phase3 -> Recovery.Rcvrlock**

所有的configured lanes工作在最佳的工作模式,8 GT

所有的configured lanes工作在最佳的工作模式,且收到两个连续 Retimer Equalization Extend Bit = 0的TS1 序列 16 GT

设置相应速率的phase3_ successfull = 1 and complete bit =1。

phase3-> Recovery.Speed

上述两个条件未满足,24~26ms超时后调整。 [successful_speed_negotiation=0,当前speed的complete bit = 1]。

3 Upstream

upstream 比downstream 多了一个phase0,一共包含phase0 phase1 phase2 phas3 四个阶段。

3.1 Phase0

在此阶段会清除当前速率(8GT or 16 GT)的EQ_phase_successfullz指示位,同时也会设置start_equalization_w_preset = 0。

当从2.5 or 5 GT -> 8GT时候,EP会使用在Recovery.RcvrCfg阶段的EQ TS2 order set (序列)中的Transmitter Preset field填充当前需要发送的TS1序列。当从8GT -> 16GT时,EP会使用8GT EQ TS2 序列中的Transmitter Preset field进行填充,如果收到的preset 字段是非法,则由实现者决定发送什么东西。

在该子状态会首先发送EC=00 的TS 序列,对于一些异常情况, Transmitter Preset field的填充遵循如下规则:

1.接收到了EQ TS2 or 8GT EQ TS2 序列再Recovery.RcvrCfg 状态,但是其中相应preset 字段RC 不支持,则待发送的preset使用EQ序列中解析出来的transmitter preset 进行填充,Coeffiient 由实现者指定,并且set Reject Coefficient bit = 1。

2.对于未收到EQ TS2 or 8GT EQ TS2 序列,则待发送的preset and coefficent 根据由实现者自行指定,并且clear Reject Coefficient bit。

note:如果RC需要调整自己Receiver 则允许在phase1 等待500ns后,再去评估接收到的TS1 order set。

phase0 -> phase1

接收到两个连续的EC=01的TS1 order set。[LF FS 需要存储起来,放在phase2 使用;必须保证在2ms内可以完成bit lock 并可以稳定识别 Order set]。

phase0 -> Recovery.Speed

上述两个条件未满足,12ms超时后调整。 [successful_speed_negotiation=0,当前speed的complete bit = 1]

3.2 Phase1

phase1 会根据phase0 决定的transmitter setting 构造TS1 序列,并设置EC=01b。

phase1 -> phase2

接收到两个连续的EC=10的TS1 序列,并设置相应速率的phase1 successful =1。

phase1 -> Recovery.Rcvrlock

接收到连个连续的EC=00的TS1序列,并设置相应速率的phase1 successful = 1。

phase1 -> Recovery.Speed

上述两个条件未满足,12ms超时后调整。 [successful_speed_negotiation=0,当前speed的complete bit = 1]。

3.3 Phase2

会通过Receiver 接收到的TS 序列完成信号的评估,并向RC(Downstream)请求相应的参数,在该子状态TX会持续发送EC=11的TS1 order set,会根据接收的TS1 order set评估信号质量,并向RC请求新的preset 和相关系数。若 Preset bit =1,此时是一个Preset 更改请求,否则是 Cursor 系数请求。另外协议要求EP必须持续请求1us(也就是说1us后才可以更新发送的preset),等待500+ns后,EP会使用RC请求的值填充子的TS1 序列的相应字段,并发送给EP。

从请求到最终完成均衡一般不允许超过2ms,但是可以允许以同样的参数第二次尝试(此时的超时时间可以超过2ms但是不能超过24ms的状态超时),所有的lanes需要同时发送new preset and 系数,但是如果其中一些lane不需要改变当前设置,也是允许保持当前值不变继续发送。

3.4 Phase3

会发送EC=11的TS1 序列,与RC phase2 类似 此时EP会根据RC的请求调节自身的Transmitter参数。

phase3 -> Recovery.RcvrLock

所有的lanes 均收到两个连续的EC=00的TS1 序列,这表示RC已经从phase3 退出进入了RcvrLock 子状态,EP需要将相应速率下的Phase3 successful and Complete bit 置1.

phase3 -> Recovery.Speed

上述两个条件未满足,32ms超时后调整。 [successful_speed_negotiation=0,当前speed的complete bit = 1]。