verilog语法进阶-分布式ram

概述:

FPGA的LUT查找表是用RAM设计的,所以LUT可以当成ram来使用,也并不是所有的LUT都可以当成ram来使用,sliceM的ram可以当成分布式ram来使用,而sliceL的ram只能当成rom来使用,也就是只能读,不能写,它的写叫做编程,只有在上电加载程序的时候能够写。在运行的过程不可以修改。FPGA是由阵列CLB构成的,每个CLB由4个slice组成,每个slice包含一个LUT,每个LUT4可以看错是一个16x1的ram,这些小的ram也以阵列的形式排列在FPGA内部,故而称为分布式ram,对于一大块RAM,也就是具有16kbit的ram称为块ram,一般FPGA内部有几十个块ram,几千个分布式ram,根据FPGA的型号来确定。

分布ram的作用,用作数组使用,常用于小的配置文件或者配置参数,不必申请块ram,块ram往往用于存放大量数据。

内容:

1. 单端分布式ram

代码

分布式ram定义语句:

(* RAM_STYLE="{AUTO | DISTRIBUTED | PIPE_DISTRIBUTED}" *)

reg [RAM_WIDTH-1:0] dram [(2**RAM_ADDR_BITS)-1:0];

其中,RAM_WIDTH为位的宽度,(2**RAM_ADDR_BITS)-1为位的深度,是2**n。

访问方式dram[address],address是地址线,相当于数组的序号,从0开始。

dram[address]位于等式坐标,表示写地址,位于等式右边表示读,支持读写不同地址。也就是双端口

module regtest(input clk,input write_enable,input [4-1:0] input_data,output [4-1:0] output_data,input [5-1:0] address);parameter RAM_WIDTH = 4;

parameter RAM_ADDR_BITS = 5;(* RAM_STYLE="{AUTO | DISTRIBUTED | PIPE_DISTRIBUTED}" *)

reg [RAM_WIDTH-1:0] dram [(2**RAM_ADDR_BITS)-1:0];always @(posedge clk)if (write_enable)dram[address] <= input_data; // 写数据assign output_data = dram[address]; //读数据endmodule

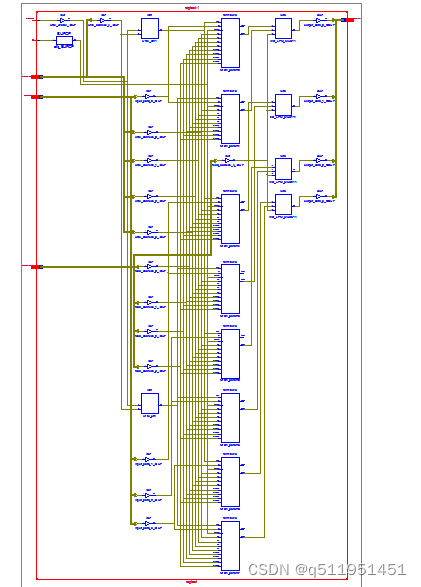

RTL结构图,结构图看上去很复杂,其实就是译码器+锁存器,译码器就是选择地址线,控制锁存器的使能端,锁存器用于存放的具体数据。

技术原理图,技术原理图上就很简单了,是FPGA以及设计好了的4pian32x1的ram。

2. 双端分布式ram

代码

module regtest(input clk,input write_enable,input [4-1:0] input_data,output [4-1:0] output_data,input [5-1:0] write_address,read_address);parameter RAM_WIDTH = 4;

parameter RAM_ADDR_BITS = 5;(* RAM_STYLE="{AUTO | DISTRIBUTED | PIPE_DISTRIBUTED}" *)

reg [RAM_WIDTH-1:0] ddram [(2**RAM_ADDR_BITS)-1:0];always @(posedge clk)if (write_enable)ddram[write_address] <= input_data;assign output_data = ddram[read_address]; endmodule

RTL结构图

技术原理图

总结

1. 分布式ram是由LUT查找表构成,查找表是阵列排列的,因此分布式ram也是阵列排列的,故而称为分布式ram

2.. 分布式ram的定义 (* RAM_STYLE="{AUTO | DISTRIBUTED | PIPE_DISTRIBUTED}" *)

reg [RAM_WIDTH-1:0] dram [(2**RAM_ADDR_BITS)-1:0];

3. 分布式ram的读写操作可以分开,也就是读地址线和写地址写分开,构成双口ram形式。