【上海大学数字逻辑实验报告】二、组合电路(一)

一、 实验目的

- 熟悉TTL异或门构成逻辑电路的基本方式;

- 熟悉组合电路的分析方法,测试组合逻辑电路的功能;

- 掌握构造半加器和全加器的逻辑测试;

- 学习使用可编程逻辑器件的开发工具 Quartus II设计电路。

二、 实验原理

- 异或门是数字逻辑中实现逻辑异或的逻辑门,其功能是若两个输入的电平相异,则输出高电平;若输入的两个电平相同,则输出为低电平。

- TTL异或门的输入输出电压关系:

| 输入 | 输出 | |

|---|---|---|

| A | B | Y |

| 0V | 0V | 0V |

| 0V | 5V | 5V |

| 5V | 0V | 5V |

| 5V | 5V | 0V |

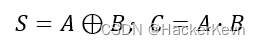

- 半加器是对两个一位二进制数进行相加,产生“和”与“进位”。其逻辑表达式为:

根据半加器的逻辑表达式可知,半加器可用一个异或门和两个与非门组成。 - 全加器是将两个一位二进制数及来自低位的进位进行相加,产生“和”与“进位”。其逻辑表达式为:

根据全加器的逻辑表达式可知,全加器可用两个异或门和三个与非门组成。

三、实验内容

实验任务一:异或门逻辑功能测试

(1) 实验步骤

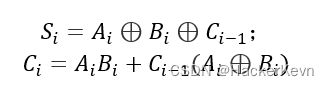

- 将74LS86的输入引脚1A连接到K1,1B连接到K2,输出引脚连接到数码管LED6,接电接地后的示意图如下所示:

- 拨动开关,观察数码管的变化,填入异或门的输入与输出状态记录表。

(2) 实验现象

- 当两个输入引脚的电平相同时,异或门的输出为逻辑低电平(0)。

- 当两个输入引脚的电平不同时,异或门的输出为逻辑高电平(1)。

(3) 数据记录、分析与处理

异或门的输入输出状态记录表

| 输入A | 输入B | 输出Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

(4) 实验结论

异或门的输出只有在两个输入的电平不同时才输出高电平,否则输出低电平。

实验任务二:使用分立元件的异或门和与非门分别构成半加器和全加器,并进行测试

(1) 实验步骤

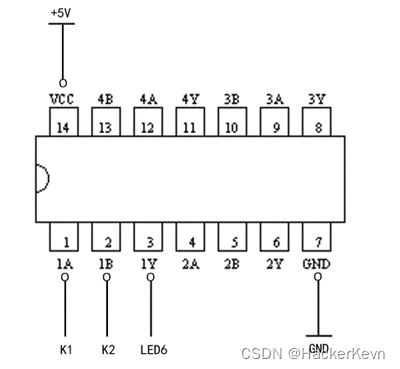

a) 构成半加器

- 将K3、K4分别对应连接到74LS86和74LS00的输入引脚1B、1A;

- 将74LS00的输出引脚1Y同时连接到74LS00的输入引脚2A、2B,而后将74LS00的输出引脚2Y连接到LED6;

- 将74LS86的输出引脚1Y连接LED5。

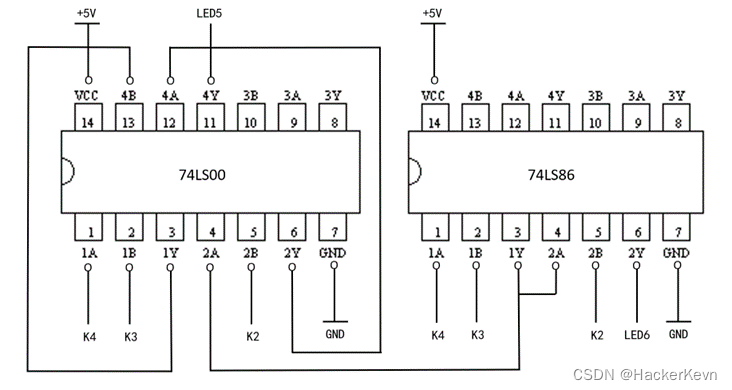

- 接地接电后的示意图如下所示:

- 拨动开关,观察数码管的变化,填入半加器的输入与输出状态记录表。

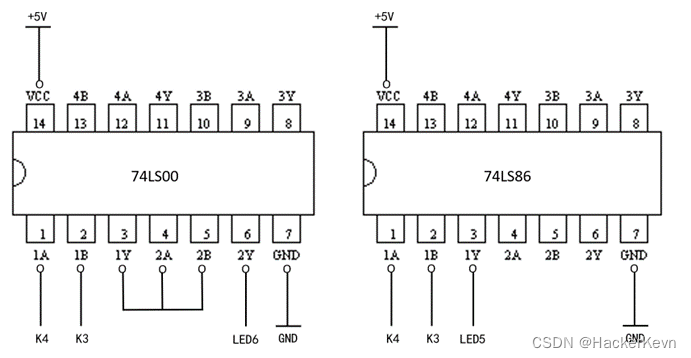

b) 构成全加器

- 将K2、K3、K4分别对应连接到74LS86和74LS00的输入引脚2B、1B、1A

- 将74LS00的输出引脚1Y、2Y、4Y分别连接到74LS00的输入引脚4B、4A、LED5;

- 将74LS86的输出引脚1Y连接到74LS00的输入引脚2A同时连接到74LS86的输入引脚2A,而后将74LS86的输出引脚2Y连接到LED6。

- 接地接电后的示意图如下所示:

- 拨动开关,观察数码管的变化,填入一位全加器的输入与输出状态记录表。

(2) 实验现象

a) 半加器

- 当输入K3、K4都为逻辑低电平(0)时,LED5和LED6都不亮;

- 当输入K3、K4有一个为逻辑高电平(1)时,LED5会亮而LED6不亮;

- 当输入K3、K4都为逻辑高电平(1)时,LED5和LED6都亮。

b) 全加器

- 当输入K2为逻辑低电平(0),拨动K3、K4开关,发现LED5和LED6的亮灭情况和半加器一致;

- 当输入K2为逻辑高电平(1)时,拨动K3、K4开关,发现当K3、K4都为逻辑低电平(0)时,发现LED6会亮而LED5不亮;当K3、K4逻辑电平相反时,发现LED6不亮而LED5会亮;当K3、K4都为逻辑高电平(1)时,发现LED6和LED5都会亮。

(3) 数据记录、分析与处理

半加器的输入输出状态记录表:

| 输入 | 输出 | ||

|---|---|---|---|

| K4 | K3 | LED6 | LED5 |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

全加器的输入输出状态记录表:

| 输入 | 输出 | |||

|---|---|---|---|---|

| K2 | K3 | K4 | LED6 | LED5 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

(4) 实验结论

a) 半加器可实现两个一位二进制数相加,输出一个结果位和进位。

b) 一位全加器可以处理低位进位,并输出本位加法进位。

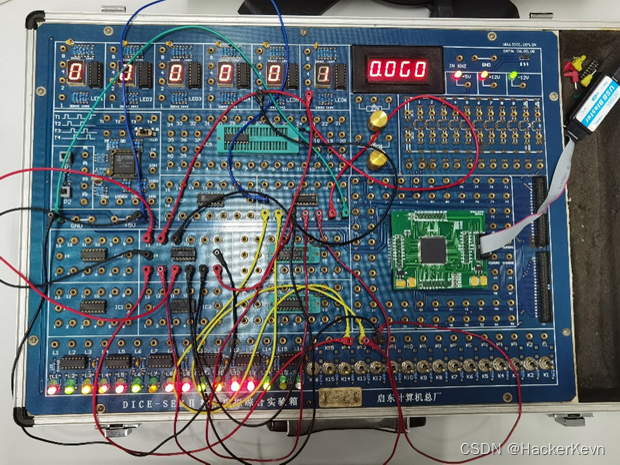

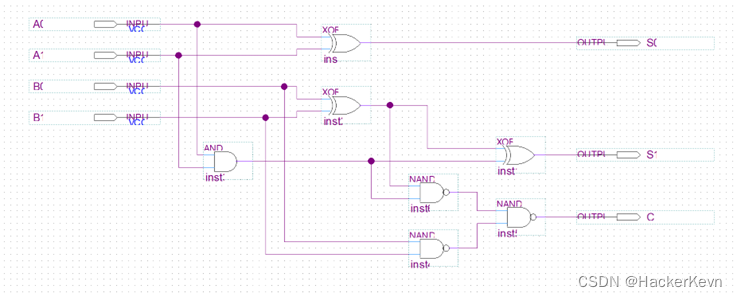

实验任务三:使用Quartus II设计二位全加器

(1) 实验步骤

- 用Quartus II设计出如下电路:

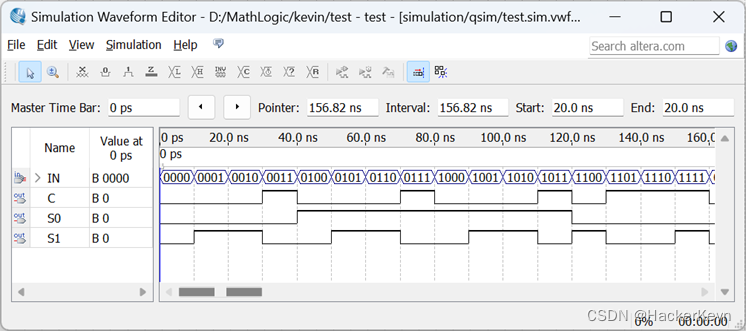

- 编译通过后进行波形仿真,验证二位全加器逻辑功能:

- 仿真通过后,参照原理图定义引脚。

- 生成编程并将文件下载到FPGA。

- 用开关和发光二极管测试FPGA的功能。

- 记录测试结果。

(1) 数据记录、分析与处理

二位全机器的输入输出状态记录表

| A1 | A0 | B1 | B0 | C | S0 | S1 |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 |

(2) 实验结论

通过使用Quartus II设计工具,我们成功地设计并测试了一个二位全加器电路。该电路的功能包括正确计算两个二位二进制数的和,并产生相应的进位信号。实验结果表明,电路在各种输入条件下都表现出良好的性能,符合预期行为。

四、建议和体会

- 在进行实验时,应先确认74LS00、74LS86的功能完好,而后仔细检查芯片的引脚连接,确保连接正确,以避免电路故障。

- 实验中要确保安全,特别是在使用电源和连接线时,避免短路和电击风险。

- 这个实验有助于加深对异或门和电路设计的理解,同时也提供了一个实际的编程和模拟测试经验。为了更好地理解电路的运作,我们可以尝试设计更复杂的电路或改进现有的设计。