STM32:时钟树原理概要

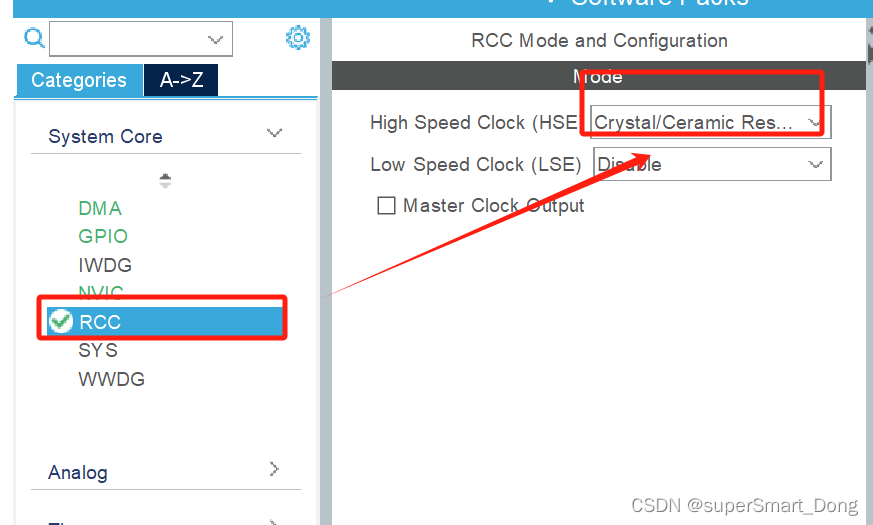

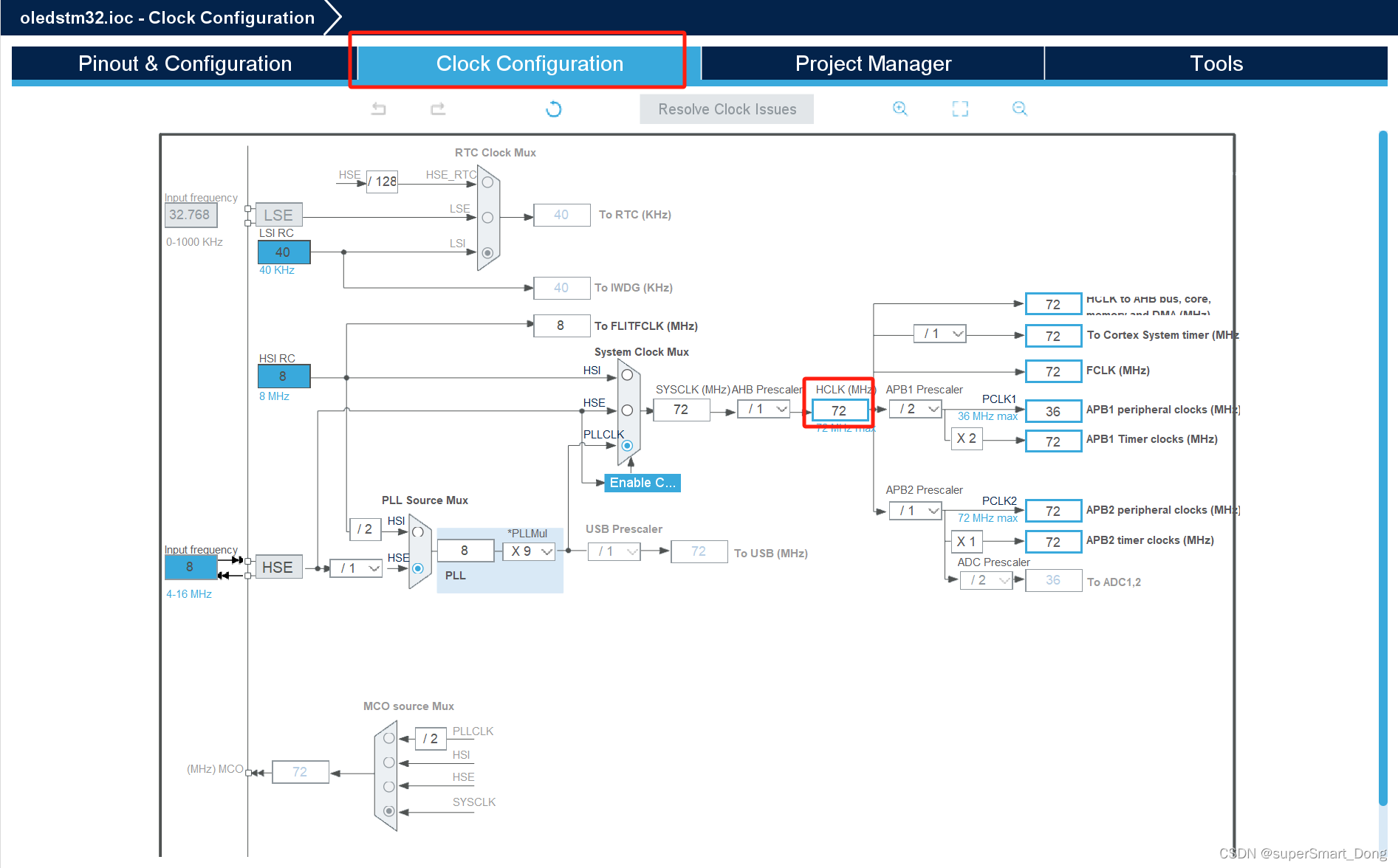

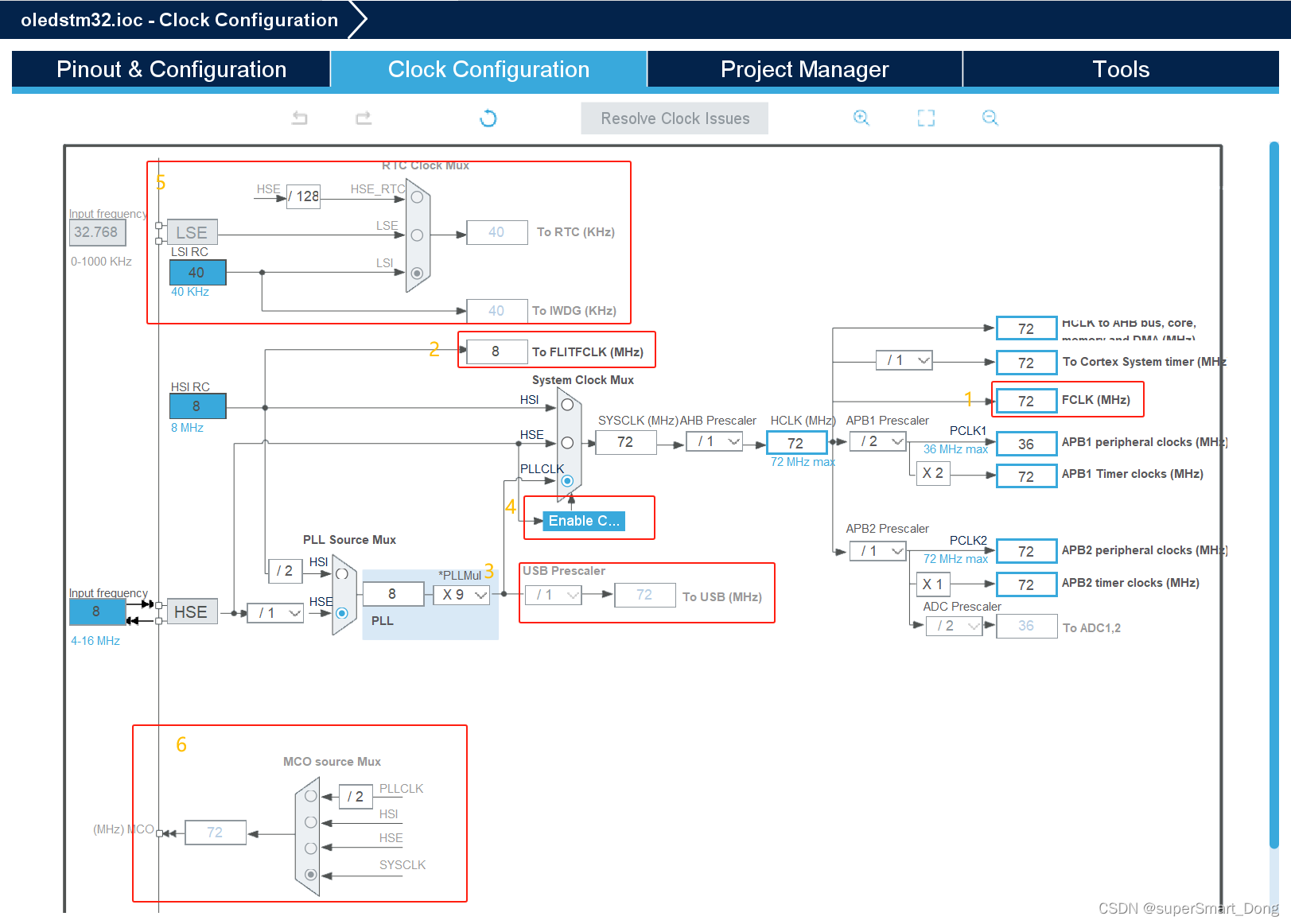

在一般情况下只要在CubeIDE中将RCC下的高速时钟源设置成晶振,随后在时钟配置中把HCLK设置到最大频率(比如STM32F103的最高频率是72MHZ ),CubeIDE就会帮我们自动调节其它参数到合适的值。这样我们芯片就可以全速运行了。

一、时钟信号

芯片大部分都是由庞大的电路组成。这种电路通常是逻辑电路。例如如下电路:

AB线路分别输入 0 和 1 后经过与门和异或门,在寄存器存的值便是 1。此时AB线路再分别输入1和1,在理想状态下寄存器值就会变成0。但是实际和理想情况不同。

在现实实践中,存在门电路运算延时问题。在AB线路分别输入1和1的时候,由于与门运算电路比较复杂,门电路运算相比其他简单线路传输时间就更长。在异或门下端输入到高电平时,上端还保留上次与门运算的输出结果,此时就会处于一种由延迟造成的错误状态。处在这种错误状态时间虽然短暂,但是依赖于这种电路组成的复杂系统可能会在不可预知的时间内发生不可预知的错误。

为了解决这种延迟问题可以在电路中引入边沿触发器。边沿触发器中包含一个输入端(D),输出端(Q),和控制端(CLK).边沿触发器的特性:将一个固定频率的信号不断发送到控制端中。在控制端出现一个从低电平到高电平的上升沿信号时,才会将输入结果从输出端输出。电路修正为如下图所示,这种固定频率的方波信号,可以在一个完整周期内保证寄存器的值都不会改变,解决了电路运算延时问题。这种方波信号就是时钟信号。

时钟信号由单片机“心脏”时钟源产生,通过“动脉”时钟树传播到整个芯片电路中。

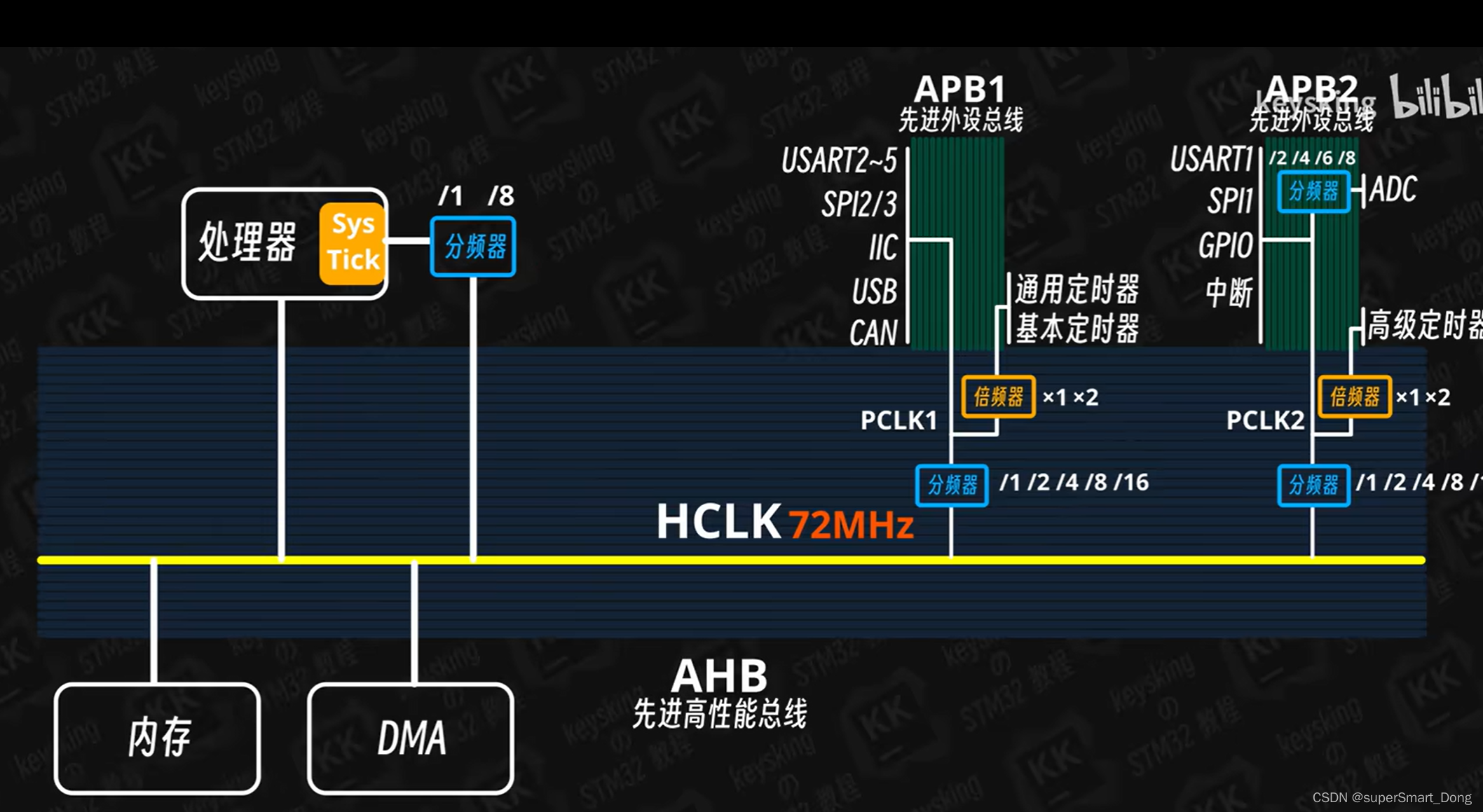

二、HCLK 时钟树

在STM32内部有一个叫做先进高性能总线(Advance High Performance Bus,AHB)总线。它就是STM32的主干道。STM32芯片中的处理器,内存,DMA,以及各种外设都连接到这一总线上。

HCLK属于AHB总线中的时钟线。它直接连接了处理器,内存,DMA。为他们带去了时钟信号。在处理器内核中有一个成为 SysTick(系统滴答)的定时器,为我们的程序提供一个时钟基准(HAL_DELAY()函数就是依赖于SysTick)。与直连不同,SysTick和AHB之间连接了一个分频器

分频器的作用是变频,降低频率。即给频率作除法。例如将分频器设置为"/8"也就是变成原来频率的1/8。连接SysTick的分频器可以设置“/1”和“/8”。例如AHB提供72MHZ的频率经过"/8"的分频器后就会变成9MHZ。

在STM32芯片中,像GPIO,串口,IIC等外设并没有直接连接到AHB总线上。而是两个先进外设总线(Advance Peripheral Bus,APB)分别连接到AHB上。外设通过一种桥接器连接到APB进行处理。让外设和AHB直连的部件进行间接通信。 APB1上连接了串口2到5,SPI2/3.IIC,USD,CAN,通用定时器,基本定时器等等;APB2上连接了ADC,串口1,SPI1,高级定时器TIM1和TIM8,所有GPIO口和中断等。

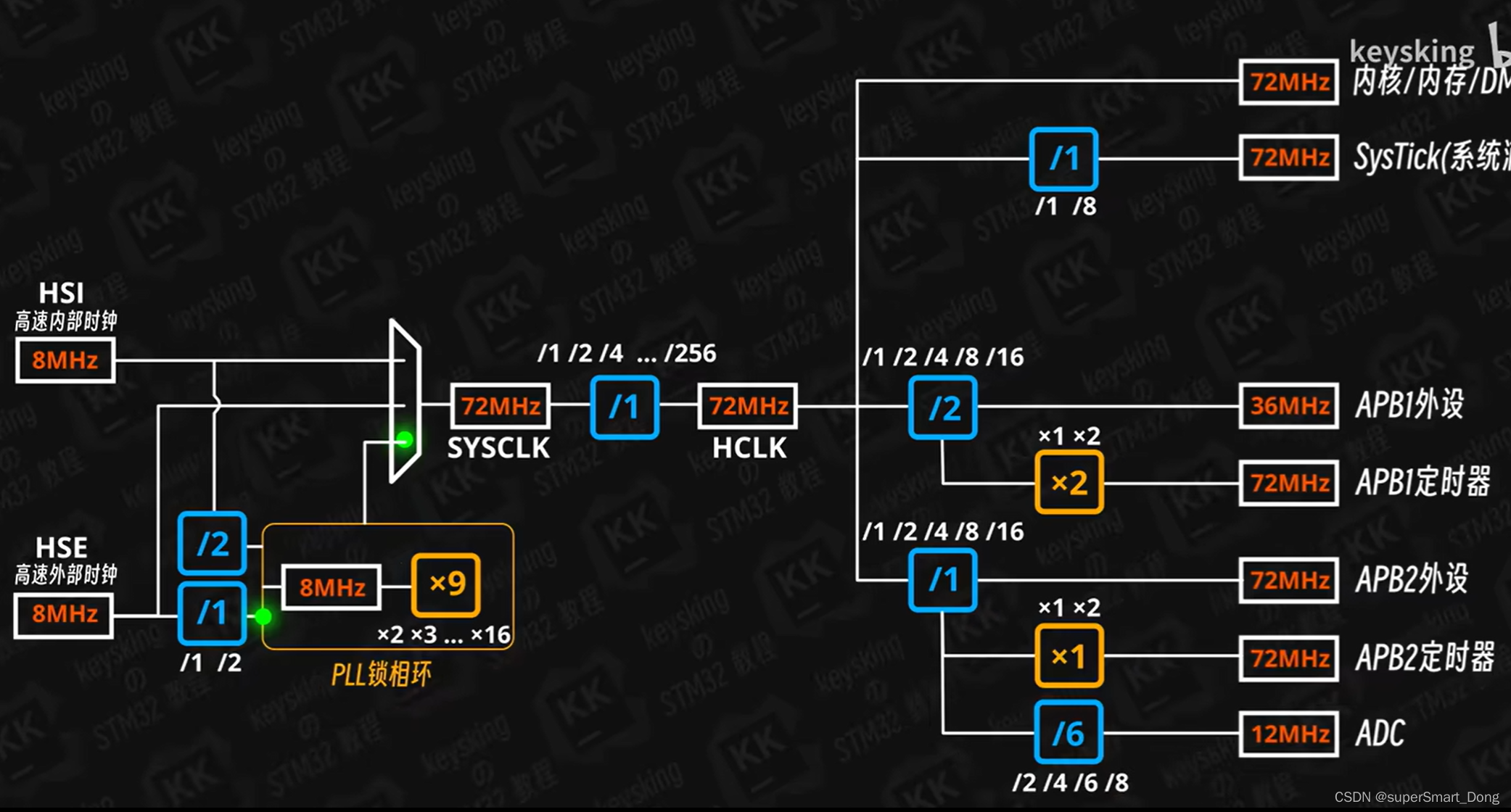

在APB1和AHB中间有一个也有一个分频器,此分频器输出的信号称作PCLK。分频器与定时器之间还连接一个倍频器。倍频器与分频器的功能相反,用来给频率作乘法。例如提供32MHZ的频率经过"x2"的倍频器后就会变成72MHZ。

注:在《STM32官方参考手册》中的第2章存储器和总线构架中可以了解具体AHB总线的结构。

把上图简化成树形结构如下图HCLK的右半部分所示结构。只要设置HCLK频率再调节变频器和倍频器就可以将想要的时钟频率输出给其他部件。

从“源头”来讲,提供给HCLK的时钟源有两个,HSI高速内部时钟和HSE高速外部时钟。其中HSI是STM32的默认时钟源,它内置在芯片内部,无需外接电路,产生的频率为8MHZ。高速外部时钟HSE需要从外部电路接入一种叫做“晶振”的器件,该器件内部有石英晶体可以发出一定频率的脉冲信号,其脉冲精度要比HSI好得多。

PLLCLK锁相环时钟,它起到的作用是倍频器作用,它可以选择将HSI或者HSE的时钟分频后的信号选择一个再进行倍频输出。因此进入系统时钟SysCLK就可以有三种输入选择:HSI,HSE,PLL锁相环。再经过AHB分频器就到了HCLK部件了。

三、时钟配置补充

- FCLK,自由运行时钟:当我们需要节省电量需要STM32进行低功耗模式之一的“停止模式”时,AHB总线会停止运行,HCLK会停止传输时钟脉冲,所有连接到AHB总线上的外设都会停止运行。FCLK实际上连接是AHB分频器,当STM32处于休眠状态是,FCLK依旧处于运行态,为中断采样提供时钟信号

- To FLITFCLK:为Flash编程接口的时钟,它的时钟源永远来自于HSI。

- To USB:为USD功能提供的系统时钟,来自于PLL锁相环。

- Clock Security System,CSS时钟安全系统:原始时钟源为HSE或为倍频过的HSE可选择开启。它可以在HSE发生故障时,立即将时钟源切换为HSI,并且产生中断。

- RTC/看门狗时钟树:一个独立的时钟树,时钟源是低速内部时钟LSI和低速外部时钟LSE,或者高速外部时钟的“/128”分频。挂在上面的是RTC实时时钟和看门狗。

- Master Clock Output,时钟输出功能:在基本设置->System Core->RCC 界面中勾选Master Clock Output 就可以使用该功能。PA8引脚就会被设置为RCC_MCO。在根据时钟配置界面中选择其中一个时钟信号输出,PA8就可以获取到数据