「Verilog学习笔记」用优先编码器①实现键盘编码电路

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

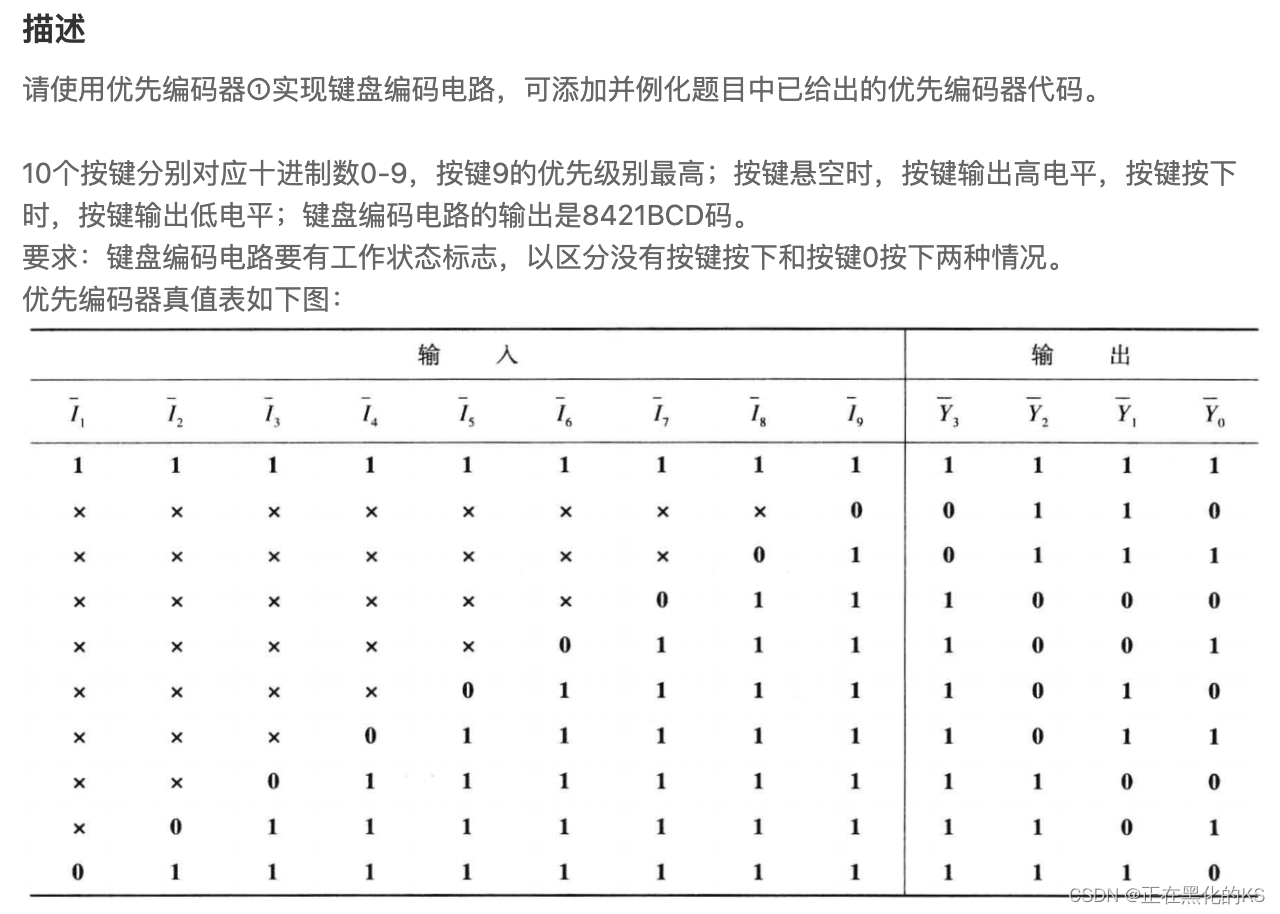

分析

用此编码器实现键盘的编码电路。

注意:编码器的输出是低电平有效,而键盘编码电路输出的是正常的8421BCD码,是高电平有效。因此将编码器的输出取反就是8421编码输出的结果

S_n[0]~S_n[9]表示10个按键,分别对应编码器的10个输入端,工作状态用GS表示,当有按键按下时,GS是1,当无按键按下时,GS是0.

需要考虑的是如何将10个按键对应到编码器的9个输入端。

仅有一种情况GS为0 即Y_n的四位均为1且S_n[0]也为1 即所有按键都没按下

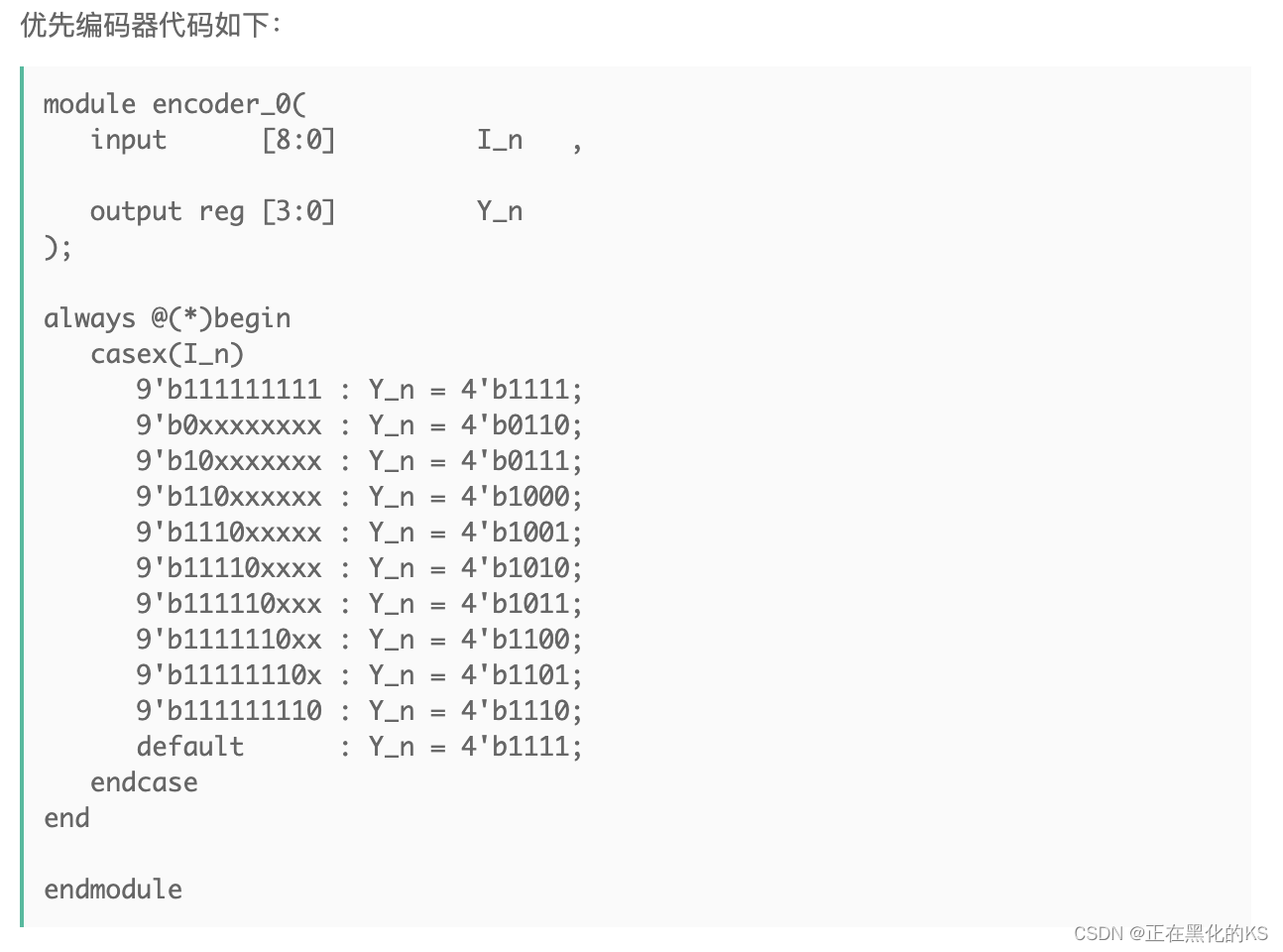

`timescale 1ns/1ns

module encoder_0(input [8:0] I_n ,output reg [3:0] Y_n

);always @(*)begincasex(I_n)9'b111111111 : Y_n = 4'b1111;9'b0xxxxxxxx : Y_n = 4'b0110;9'b10xxxxxxx : Y_n = 4'b0111;9'b110xxxxxx : Y_n = 4'b1000;9'b1110xxxxx : Y_n = 4'b1001;9'b11110xxxx : Y_n = 4'b1010;9'b111110xxx : Y_n = 4'b1011;9'b1111110xx : Y_n = 4'b1100;9'b11111110x : Y_n = 4'b1101;9'b111111110 : Y_n = 4'b1110;default : Y_n = 4'b1111; // 若0被按下 Y_n会赋值为默认值endcase

end endmodulemodule key_encoder(input [9:0] S_n , output wire[3:0] L ,output wire GS

);wire [3:0] Y_n ; encoder_0 u0 (.I_n (S_n[9:1]), .Y_n (Y_n) );assign L = ~Y_n ; assign GS = ~(S_n[0] & Y_n[0] & Y_n[1] & Y_n[2] & Y_n[3]) ;endmodule