Xilinx FPGA平台DDR3设计详解(一):DDR SDRAM系统框架

DDR SDRAM(双倍速率同步动态随机存储器)是一种内存技术,它可以在时钟信号的上升沿和下降沿都传输数据,从而提高数据传输的速率。DDR SDRAM已经发展了多代,包括DDR、DDR2、DDR3、DDR4和DDR5,每一代都有不同的特性和性能。DDR SDRAM系统包含DDR控制器、DDR PHY和DRAM存储颗粒,下面开始分别介绍这三个部分。

一、DDR 控制器

DDR控制器是连接CPU和DDR SDRAM的桥梁,负责生成控制信号来管理读写操作。控制器需要实现命令队列重排序、银行管理、功率管理等功能。

内存控制器接收来自于一个或者多个请求,由仲裁器来决定这些请求的优先级,生成对应的命令序列放置在内存控制器中的队列池(Queue pool)中,内存控制器依次执行队列池的命令,并将逻辑地址转化为物理地址,再经由PHY驱动DRAM的物理IO口。

1、Arbitration CMD priority(仲裁器)

仲裁读写请求的优先级,根据优先级进行处理,从而确定如何向控制器发出请求的顺序。

2、DDR SDRAM Control (控制器)

接受来自仲裁器的命令,并形成一个命令队列。

这个命令队列通过重排算法来决定命令的放置顺序,常用的规则有:地址碰撞、源碰撞、数据碰撞、命令类型和优先级,这样来确定命令插入到命令队列的位置。

当命令进入命令队列后,控制器的选择逻辑扫描命令队列中的命令,优先执行高优先级的命令。

如果较高优先级的命令未准备好,则较低优先级的命令可以先于这个未准备好的高优先级命令运行。

3、Transaction Processing(执行器)

用于处理命令队列中的命令,支持重排命令,以使DRAM的读写带宽吞吐达到最大化。

二、DDR PHY

DDR PHY是连接DDR DRAM颗粒和DDR Controller的桥梁,负责把DDR Controller发过来的数据转换成符合DDR协议的信号,并发送到DDR颗粒。另一方面,它也负责把DRAM发过来的数据转换成符合DFI协议的信号并发送给内存控制器。

具体来说,DDR PHY具有以下功能:

1、初始化

DDR PHY负责进行初始化,包括training等过程,确保DDR颗粒能够正常工作。

2、数据传输

DDR PHY将DDR Controller发送的数据转换为符合DDR协议的信号,并将这些信号发送到DDR颗粒。同时,它也将DRAM发送的数据转换为符合DFI协议的信号,并将这些信号发送给内存控制器。

3、寄存器管理

DDR PHY提供了一些寄存器,用于配置和管理DDR颗粒的参数,如时序、电压等。

错误检测与处理:DDR PHY还负责进行错误检测和处理,确保数据传输的正确性。

DDR PHY和DDR controller统称为DDR IP,他们保证了SoC和DRAM之间的数据传输。

三、DDR DRAM颗粒

DDR DRAM颗粒是DDR系统中的存储单元,每个单元由一个电容和晶体管组成,用来存储一个bit的数据。

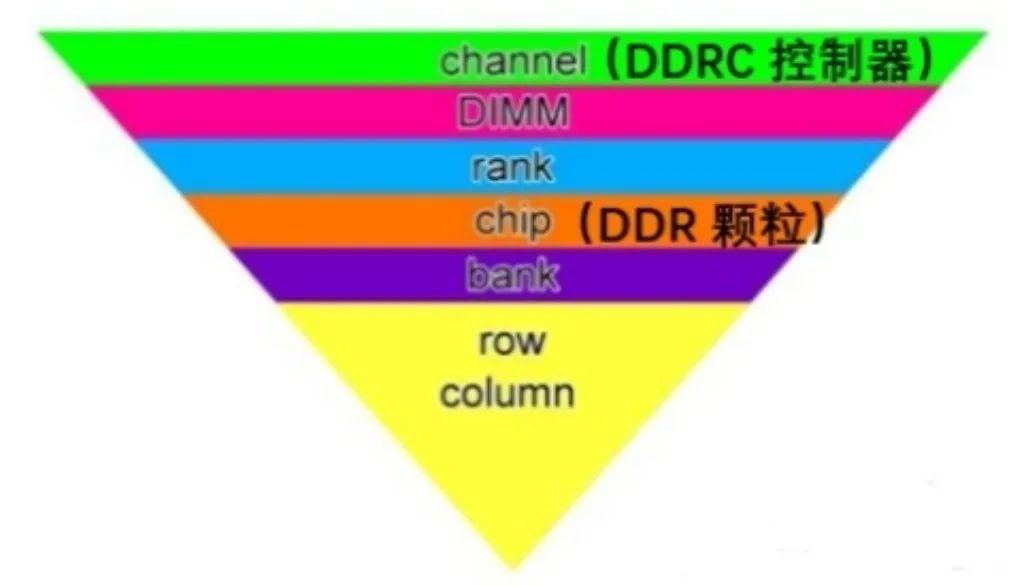

1、DDR PHY到DDR内存颗粒的层次关系

channel->DIMM->rank->chip->bank->row/column组成的memory array

2、详细解释

(1)Channel

一个通道对应一个DDR控制器,每个通道拥有一组地址线、控制线和数据线。

(2)DIMM

主板上的一个内存插槽,一个channel可以包含多个DIMM。

(3)Rank

一组可以被一个内存通道同时访问的芯片组合称作一个rank,一个rank中的每个芯片都共用内存通道提供的地址线、控制线和数据线,同时每个芯片都提供一组输出线,这些输出线组合起来就是内存条的输出线。

简单理解,rank是一组内存芯片集合,一个Rank的内存总位宽等于芯片位宽*芯片数, 64bit的位宽,即表示一般每个芯片位宽是8bit,然后内存条每面8个芯片,那么每面就构成了一个Rank,这两面的Rank通过一根地址线来区分当前要访问的是哪一面。

同一个Rank中所有的芯片协作来读取一个地址(1个Rank,8个芯片*8bit=64bit),这个地址的不同bit,每8个一组分散在这个Rank上的不同芯片上。设计Rank的原因是为了减少每个芯片的位宽(在CPU总位宽确定的前提下,比如64bit),降低复杂度。

(4)Chip

表示内存条上的一个芯片,由多个bank组成,大多数是4bit/8bit/16bit,多个chip做成一个rank,配合完成一次访问的位宽。

(5)Bank

这是一个逻辑上的概念。一个bank可以分散到多个chip上,一个chip也可以包含多个bank。

(6)Row、Column组成的memory array

可以简单的理解bank为一个二维bit类型的数组。每个bank对应一个bit,8个bank组成8bit的数据。

四、总结

DDR技术从最初的DDR1到当前的DDR5,通过不断提升时钟频率、传输速率和带宽等指标,大幅度改进了内存性能。DDR系统由控制器、PHY和DRAM存储单元组成,控制器负责命令调度,PHY负责信号转换,三者协同工作完成内存的读写操作。

DDR的层次结构也变得更加复杂,从channel到rank再到bank,需要各个层次的协作才能完成一次内存访问。

DDR技术的进步与计算系统性能的提升是同步的,也使我们看到内存系统的重要性。未来DDR技术仍有很大的发展空间,将继续推动计算机性能的增强。

本文将不断定期更新中,码字不易,点⭐️赞,收⭐️藏一下,不走丢哦

本文由FPGA入门到精通原创,有任何问题,都可以在评论区和我交流哦

您的支持是我持续创作的最大动力!如果本文对您有帮助,请给一个鼓励,谢谢。