高速信号PCB布局怎么布?(电子硬件)

对于高速信号,pcb的设计要求会更多,因为高速信号很容易收到其他外在因素的干扰,导致实际设计出来的东西和原本预期的效果相差很多。

所以在高速信号pcb设计中,需要提前考虑好整体的布局布线,良好的布局可以很好的决定布线的走向和结构,电源与地之间的分割,以及电磁干扰和噪声的控制。

不过在理解高速PCB设计前,需要知道什么是高速信号。

一般如果符合以下几点,那它就可以被认为是高速信号(cadence公司做的定义):

(1)频率大于50MHz的信号,就是高速信号

(2)信号是否高速不单单看频率,而是信号上升/下降沿小于50ps时就认为是高速信号

(3)当信号沿着传输路径传输,发生了严重的趋肤效应(电流集中在导线外表薄层的现象)和电离损耗时,就认为是高速信号

在布局之前,首先必须清楚系统原理图,将各个电路进行划分,比如分为数字,模拟,混合数字模拟,特别注意各芯片电源和信号引脚的位置摆放。

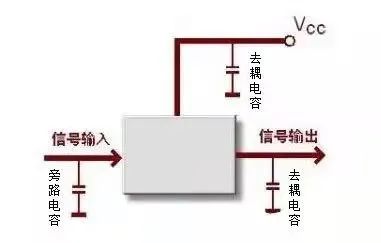

在划分完各部分电路之后,初步规划数字电路,模拟电路之后的布线区域,让各部分电路至少尽量相互远离。在实际中的布局,也会有先后顺序,依次是混合型器件==模拟器件==>数字器件==>旁路电容。

数字电路部分和模拟电路部分是一定要分开的,那混合数字模拟电路部分放哪里?

它一般需要放置在数字信号区域和模拟信号区域的交界处。

所以在摆放时,数字部分引脚尽量靠近数字电路部分,模拟部分引脚尽量靠近模拟电路部分。

对于用来产生特定频率的晶振,应尽量将相关晶振电路放置在其驱动器件旁。保证时序信号的正常,所以需要达到在下一个时钟周期到来之前,前一个数据需要能被稳定的传输和被读取。

噪声是电路设计中常见的现象,在高频高速信号设计中,对于噪声敏感的器件要远离高速信号。

旁路电容一般是用来将混有高频电流和低频电流的交流电中的高频成分滤除的,所以在旁路电路的设计中应该尽量让它靠近电源引脚放置,尤其是对于高频电路。并且在电源接口附近放置大容量电容,可以让电源保持稳定,降低噪声干扰。

良好的布局可以为pcb的布线带来事半功倍的效果。