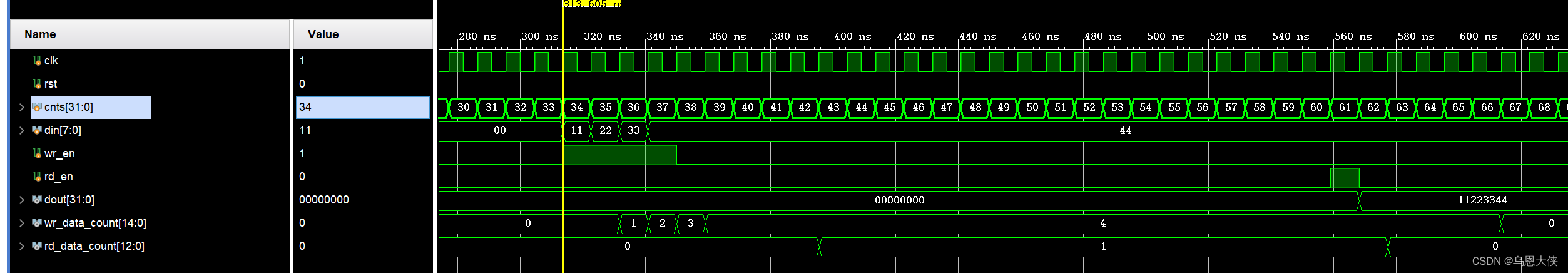

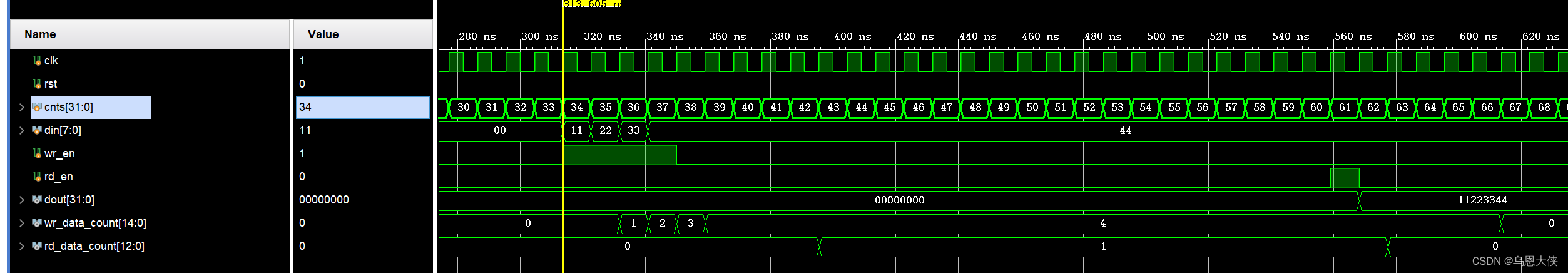

从8位转32位

module tb_fifo();reg clk,rst;

initial beginclk=0;forever #4.545 clk=~clk;

end

initial beginrst=1;#9.09 rst=0;

endreg [31:0] cnts;

always @ (posedge clk or posedge rst)

beginif(rst)begincnts <= 32'd0;endelsebegincnts <= cnts + 1'b1;end

endreg [7:0] din;

reg wr_en;reg rd_en;

wire [31:0] dout;wire [12:0] rd_data_count;

wire [14:0] wr_data_count;fifo_ICBR_8_32 FIFO (.rst(rst), .wr_clk(clk), .rd_clk(clk), .din(din), .wr_en(wr_en), .rd_en(rd_en), .dout(dout), .full( ), .empty( ), .rd_data_count(rd_data_count), .wr_data_count(wr_data_count)

);always @ (posedge clk or posedge rst)

beginif(rst)begindin <= 8'd0;wr_en <= 1'b0;rd_en <= 1'b0;endelsebegincase(cnts)32'd33: begin din<=8'h11;wr_en<=1'b1; end32'd34: begin din<=8'h22;wr_en<=1'b1; end32'd35: begin din<=8'h33;wr_en<=1'b1; end32'd36: begin din<=8'h44;wr_en<=1'b1; end32'd37: begin wr_en<=1'b0; end32'd60: begin rd_en<=1'b1; end32'd61: begin rd_en<=1'b0; enddefault:begin din<=din;wr_en<=wr_en;rd_en<=rd_en; endendcaseend

end