AD7321代码SPI接口模数转换连接DAC0832输出verilog

名称:AD7321代码12位ADC,SPI接口模数转换连接DAC0832输出

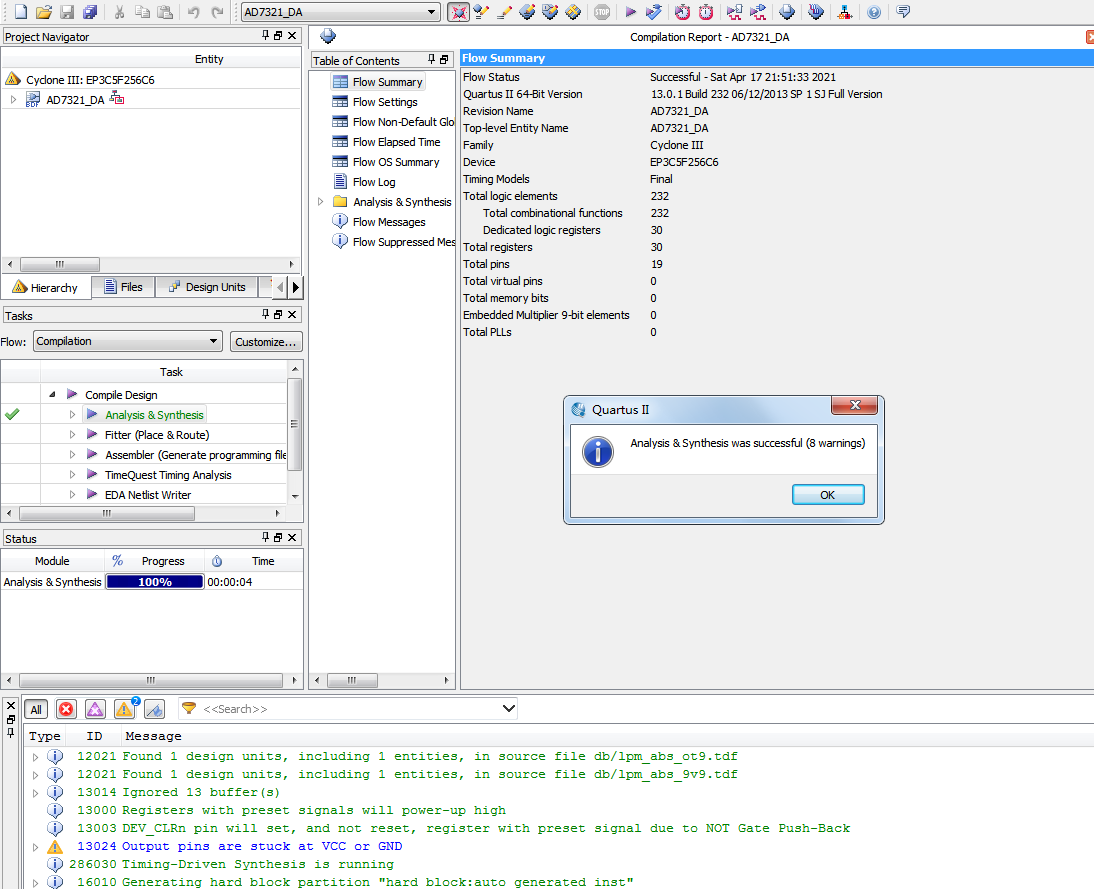

软件:QuartusII

语言:VHDL

代码功能:

使用VHDL语言编写代码,实现AD7321的控制,将模拟信号转换为数字信号,再经过处理后,将数据通过DAC0832转换为模拟信号输出

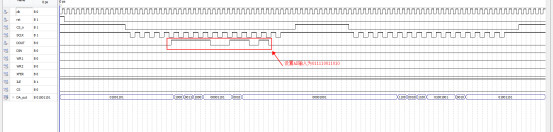

AD7321输入,(2000-输入)/6(仿真输出=009),DAC0832输出。

要求:有vhdl代码(详尽注释),有fpga连线图,有完整功能仿真结果,有方案分析。

演示视频:AD7321代码12位ADC,SPI接口模数转换连接DAC0832输出

FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com

代码下载:

AD7321代码12位ADC,SPI接口模数转换连接DAC0832输出(代码在文末付费下载)软件:QuartusII语言:VHDL代码功能:使用VHDL语言编写代码,实现AD7321的控制,将模拟信号转换为数字信号,再经过处理后,将数据通过DAC0832转换为模拟信号输出AD7321输入,(2000-输入)/6(仿真输出=009),DAC0832输出。要求:有vhdl代码(详尽注释),有fp名称:AD7321代码12位ADC,SPI接口模数转换连接DAC0832输出(代码在文末付费下载)软件:QuartusII语言:VHDL代码功能:使用VHDL语言编写代码,实现AD7321的控制,将模拟信号转换为数字信号,再经过处理后,将数据通过DAC0832转换为模拟信号输出AD7321输入,(2000-输入)/6(仿真输出=009),DAC0832输出。要求:有vhdl代码(详尽注释),有fp![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=219

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=219

部分代码展示

LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_unsigned.all; --AD控制模块,输出011110011010 ENTITY AD7321 ISPORT (clk : IN STD_LOGIC;--时钟rst : IN STD_LOGIC;--复位CS_n : OUT STD_LOGIC;--AD控制信号SCLK : OUT STD_LOGIC;--AD控制信号DOUT : IN STD_LOGIC;--AD控制信号DIN : OUT STD_LOGIC;--AD控制信号DB : OUT STD_LOGIC_VECTOR(11 DOWNTO 0)--输出AD值); END AD7321; ARCHITECTURE behaval OF AD7321 ISTYPE State_type IS (s_init, s_cs_h, s_sclk, s_end); -- 定义状态SIGNAL state : State_type;SIGNAL cs_h_cnt : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000";--CS计数SIGNAL sclk_cnt : STD_LOGIC_VECTOR(7 DOWNTO 0) := "00000000";--sclk计数 BEGIN --状态机控制PROCESS (clk, rst)BEGINIF (rst = '1') THEN--复位state <= s_init;ELSIF (clk'EVENT AND clk = '1') THEN--时钟上升沿CASE state ISWHEN s_init =>--初始状态state <= s_cs_h;WHEN s_cs_h =>--cS高电平状态IF (cs_h_cnt >= "1010") THEN--计数10个时钟state <= s_sclk;END IF;WHEN s_sclk =>--SCLK状态IF (sclk_cnt >= "00100000") THEN--计数32时钟state <= s_end;--结束END IF;WHEN s_end =>--结束状态state <= s_init;WHEN OTHERS =>END CASE;END IF;END PROCESS;--根据状态控制CS信号PROCESS (clk, rst)BEGINIF (rst = '1') THENCS_n <= '1';--复位ELSIF (clk'EVENT AND clk = '1') THEN--时钟上升沿IF (state = s_cs_h) THEN--CS高电平状态CS_n <= '1';--输出高电平ELSIF (state = s_sclk) THEN--SCLK状态CS_n <= '0';--输出低电平END IF;END IF;END PROCESS;--根据状态控制SCLK信号PROCESS (clk, rst)BEGINIF (rst = '1') THENSCLK <= '1';--复位ELSIF (clk'EVENT AND clk = '1') THEN--时钟上升沿IF (state = s_sclk) THEN--SCLK状态SCLK <= NOT(sclk_cnt(0));--SCLK输出sclk_cnt(0)取反信号作为SCLKELSIF (state = s_end) THENSCLK <= '1';END IF;END IF;END PROCESS;

设计文档:

设计文档.doc

1. 工程文件

2. 程序文件

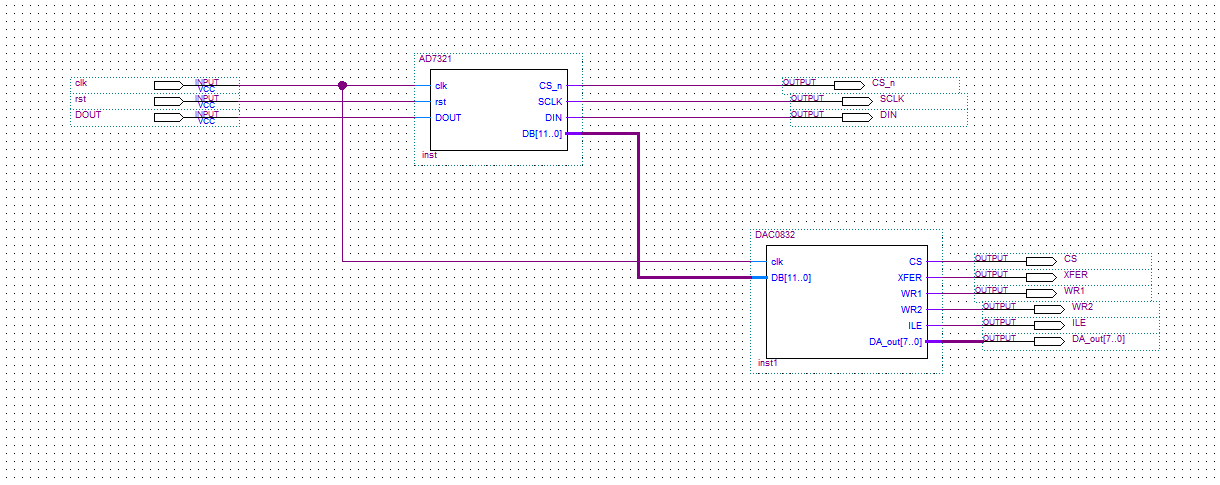

连线图

3. 程序编译

4. RTL图

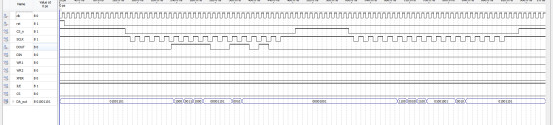

5. 仿真图