基于FPGA的电风扇控制器verilog,视频/代码

名称:基于FPGA的电风扇控制器verilog

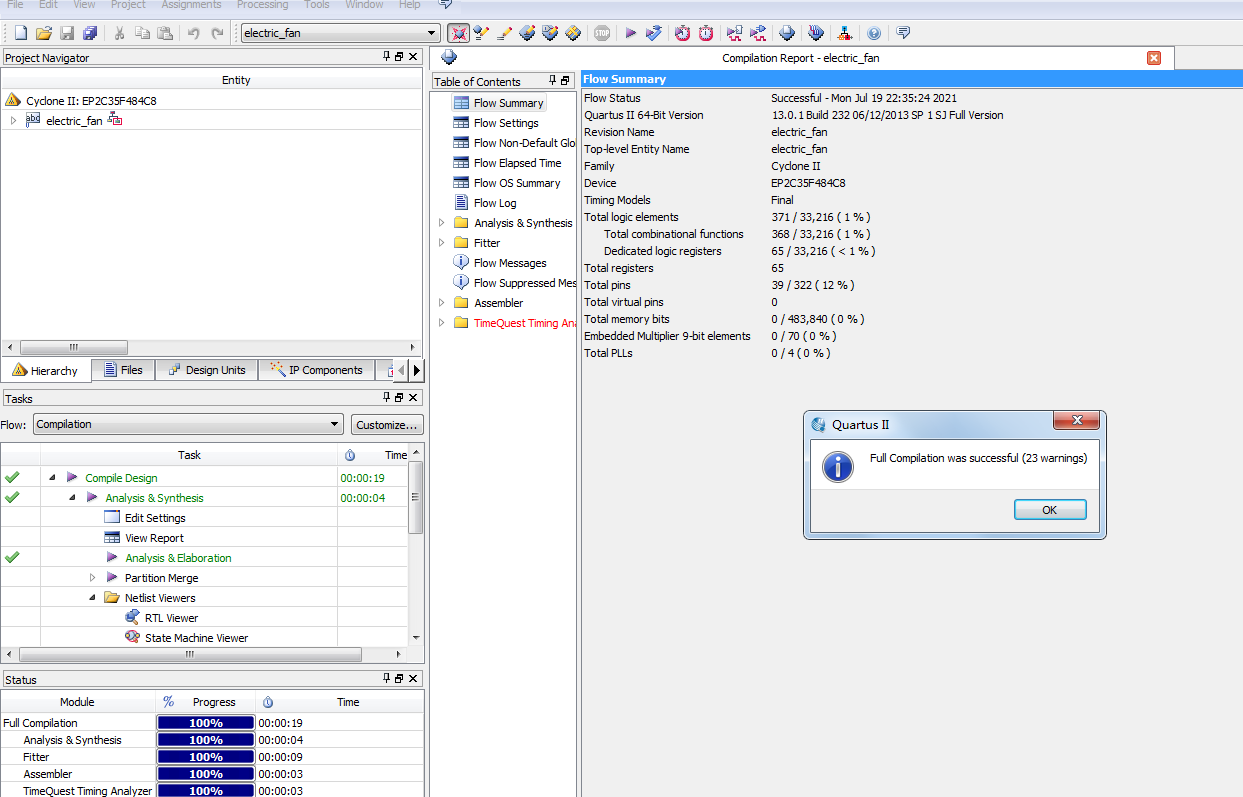

软件:QuartusII

语言:Verilog

代码功能:

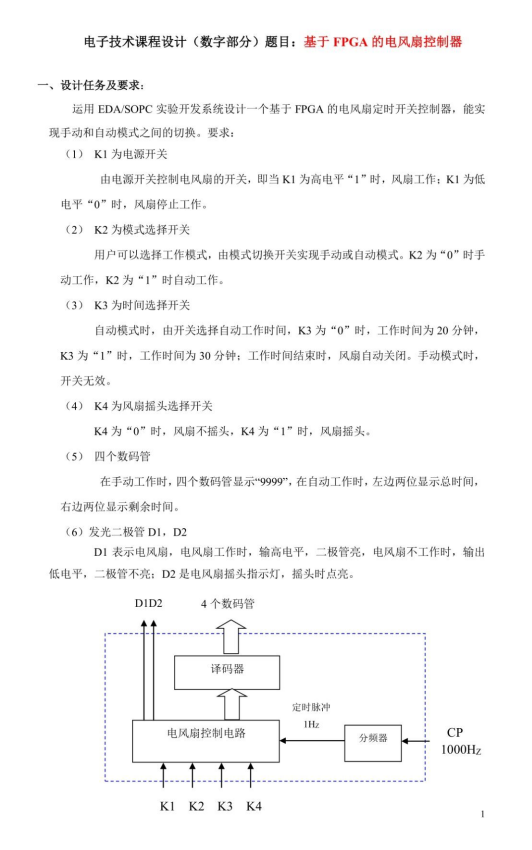

基于FPGA的电风扇控制器

运用 EDA SOPO实验开发系统设计一个基于FPGA的电风扇定时开关控制器,能实现手动和自动模式之间的切换。要求:

(1)KI为电源开关由电源开关控制电风扇的开关,即当K1为高电平“1”时,风扇工作:K1为低 电平“0”时,风扇停止工作

(2)K2为模式选择开关 用户可以选择工作模式,由模式切换开关实现手动或自动模式。K2为“0”时手 动工作,K2为“1”时自动工作

(3)K3为时间选择开关 自动模式时,由开关选择自动工作时间,K3为“0”时,工作时间为20分钟 K3为“1”时,工作时间为30分钟:工作时间结束时,风扇自动关闭。手动模式时 开关无效

(4)K4为风扇摇头选择开关 K4为“0”时,风扇不摇头,K4为“1”时,风扇摇头

(5)四个数码管 在手动工作时,四个数码管显示“9999,在自动工作时,左边两位显示总时间

(6)发光二极管D1,D2 D1表示电风扇,电风扇工作时,输高电平,二极管亮,电风扇不工作时,输出 低电平,二极管不亮:D2是电风扇摇头指示灯,摇头时点亮。

演示视频:http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=214

FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com

代码下载:

电风扇基于FPGA的电风扇控制器verilog(代码在文末付费下载)软件:QuartusII语言:Verilog代码功能:基于FPGA的电风扇控制器 运用 EDA SOPO实验开发系统设计一个基于FPGA的电风扇定时开关控制器,能实现手动和自动模式之间的切换。要求: (1)KI为电源开关由电源开关控制电风扇的开关,即当K1为高电平“1”时,风扇工作:K1为低 电平“0”时,风扇停止工作 (2)K2名称:基于FPGA的电风扇控制器verilog(代码在文末付费下载)软件:QuartusII语言:Verilog代码功能:基于FPGA的电风扇控制器 运用 EDA SOPO实验开发系统设计一个基于FPGA的电风扇定时开关控制器,能实现手动和自动模式之间的切换。要求: (1)KI为电源开关由电源开关控制电风扇的开关,即当K1为高电平“1”时,风扇工作:K1为低 电平“0”时,风扇停止工作 (2)K2![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=214

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=214

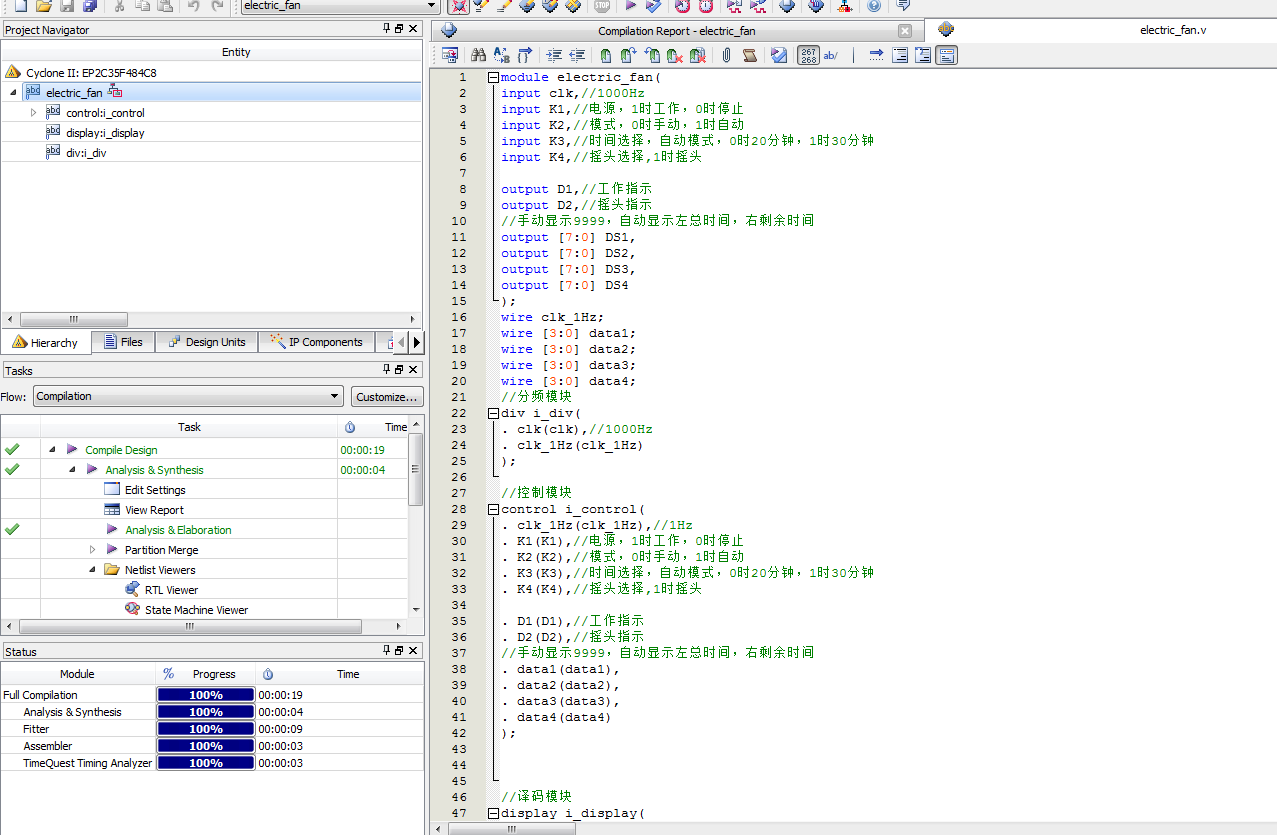

部分代码展示

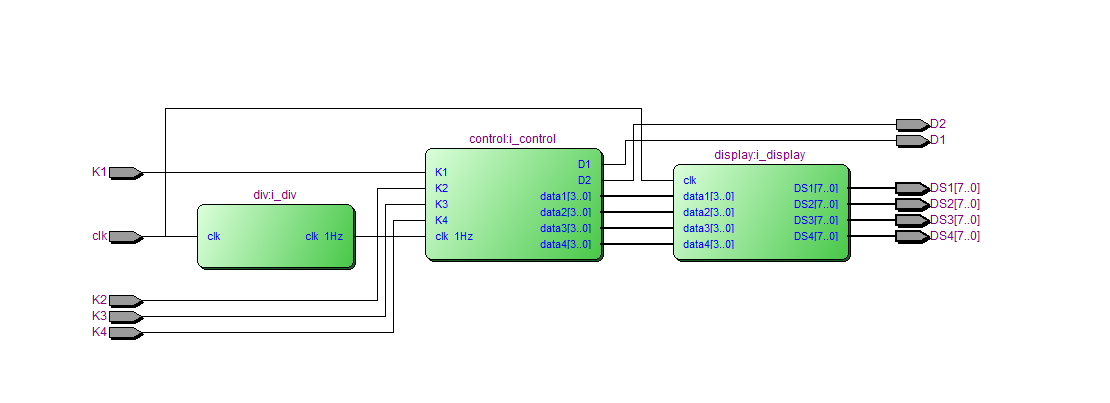

module electric_fan( input clk,//1000Hz input K1,//电源,1时工作,0时停止 input K2,//模式,0时手动,1时自动 input K3,//时间选择,自动模式,0时20分钟,1时30分钟 input K4,//摇头选择,1时摇头 output D1,//工作指示 output D2,//摇头指示 //手动显示9999,自动显示左总时间,右剩余时间 output [7:0] DS1, output [7:0] DS2, output [7:0] DS3, output [7:0] DS4 ); wire clk_1Hz; wire [3:0] data1; wire [3:0] data2; wire [3:0] data3; wire [3:0] data4; //分频模块 div i_div( . clk(clk),//1000Hz . clk_1Hz(clk_1Hz) ); //控制模块 control i_control( . clk_1Hz(clk_1Hz),//1Hz . K1(K1),//电源,1时工作,0时停止 . K2(K2),//模式,0时手动,1时自动 . K3(K3),//时间选择,自动模式,0时20分钟,1时30分钟 . K4(K4),//摇头选择,1时摇头 . D1(D1),//工作指示 . D2(D2),//摇头指示 //手动显示9999,自动显示左总时间,右剩余时间 . data1(data1), . data2(data2), . data3(data3), . data4(data4) ); //译码模块 display i_display( . clk(clk),//1000Hz . data1(data1), . data2(data2), . data3(data3), . data4(data4), //手动显示9999,自动显示左总时间,右剩余时间 . DS1(DS1), . DS2(DS2), . DS3(DS3), . DS4(DS4) ); endmodule

设计文档:

设计文档.doc

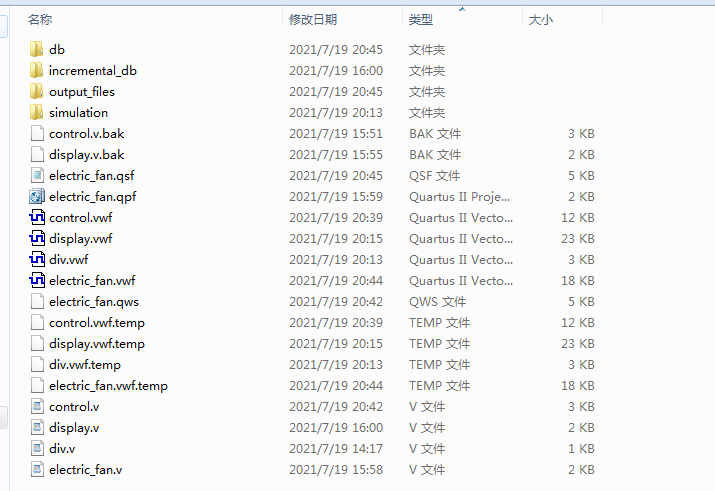

1. 工程文件

2. 程序文件

3. 程序编译

4. 管脚分配

5. RTL图

6. 仿真图

整体仿真图

分频模块仿真图

控制模块仿真图

显示模块仿真图