UVM仿真环境搭建

环境

本实验使用环境为:

Win10平台下的Modelsim SE-64 2019.2

代码

dut代码:

module dut(clk,rst_n, rxd,rx_dv,txd,tx_en);

input clk;

input rst_n;

input[7:0] rxd;

input rx_dv;

output [7:0] txd;

output tx_en;reg[7:0] txd;

reg tx_en;always @(posedge clk) beginif(!rst_n) begintxd <= 8'b0;tx_en <= 1'b0;endelse begintxd <= rxd;tx_en <= rx_dv;end

end

endmodule

其功能很简单,即将接受到的数据原封不动发送出去。

driver代码:

`ifndef MY_DRIVER__SV

`define MY_DRIVER__SV

class my_driver extends uvm_driver;function new(string name = "my_driver", uvm_component parent = null);super.new(name, parent);endfunctionextern virtual task main_phase(uvm_phase phase);

endclasstask my_driver::main_phase(uvm_phase phase);top_tb.rxd <= 8'b0; top_tb.rx_dv <= 1'b0;while(!top_tb.rst_n)@(posedge top_tb.clk);for(int i = 0; i < 256; i++) // 开始循环256次begin@(posedge top_tb.clk);top_tb.rxd <= $urandom_range(0, 255); // 随机向rxd 上发送一个0~255的随机数top_tb.rx_dv <= 1'b1; // 有效位,置1`uvm_info("my_driver", "data is drived", UVM_LOW)end@(posedge top_tb.clk);top_tb.rx_dv <= 1'b0; // 完成后有效位拉低

endtask

`endif

定义一个driver类,它派生自uvm_driver。driver的主要功能在main_phase task中实现,主要功能为向rxd管脚上发送随机数。`uvm_info(“my_driver”, “data is drived”, UVM_LOW)为打印信息的宏。

top_tb.sv:

`timescale 1ns/1ns

`include "uvm_macros.svh" // 包含宏定义import uvm_pkg::*; // 导入UVM库

`include "my_driver.sv"module top_tb;reg clk;

reg rst_n;

reg[7:0] rxd;

reg rx_dv;

wire[7:0] txd;

wire tx_en;dut my_dut(.clk(clk),.rst_n(rst_n),.rxd(rxd),.rx_dv(rx_dv),.txd(txd),.tx_en(tx_en));initial begin // 定义drv 并进行实例化my_driver drv;drv = new("drv", null);drv.main_phase(null); // 调用drive的 main_phase$finish();

endinitial beginclk = 0;forever begin#1 clk = ~clk;end

endinitial beginrst_n = 1'b0;#10;rst_n = 1'b1;

endendmodule

脚本

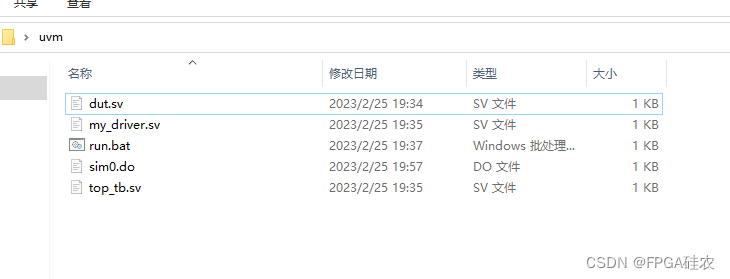

编写sim0.do脚本

cd C:/Users/xxx/Desktop/uvm

vlib work

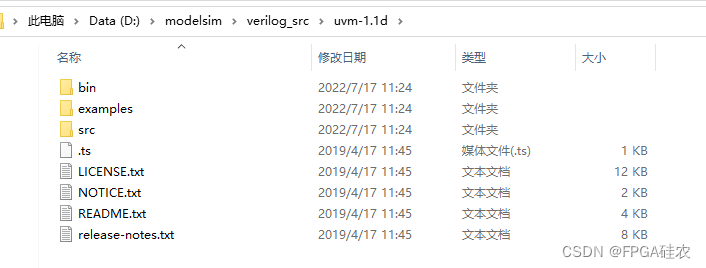

set UVM_HOME D:/modelsim/verilog_src/uvm-1.1d

set WORK_HOME C:/Users/xxx/Desktop/uvm

vlog +incdir+$UVM_HOME/src -L mtiAvm -L mtiOvm -L mtiUvm -L mtiUPF $UVM_HOME/src/uvm_pkg.sv $WORK_HOME/dut.sv top_tb.sv

vsim -c -sv_lib D:/modelsim/uvm-1.1d/win64/uvm_dpi work.top_tb

- 第一行,通过cd切换到源文件所在目录

- 第二行,vlib命令用于建立一个新的工作库。

在本例子中,vlib work在当前目录建立work工作区文件夹,运行后会在当前目录下找到work文件夹。 - 设置UVM库的路径和工作文件夹。如下图所示。

- vlog命令用于编译verilog代码,具体用法可参见博客

- vsim表示运行仿真,-sv_lib 对应uvm的一个路径。其中参数“-c”表示进入命令行模式,如果没有该参数,则表示进行GUI模式。

最后,编写run.bat文件如下

vsim -do sim0.do

运行

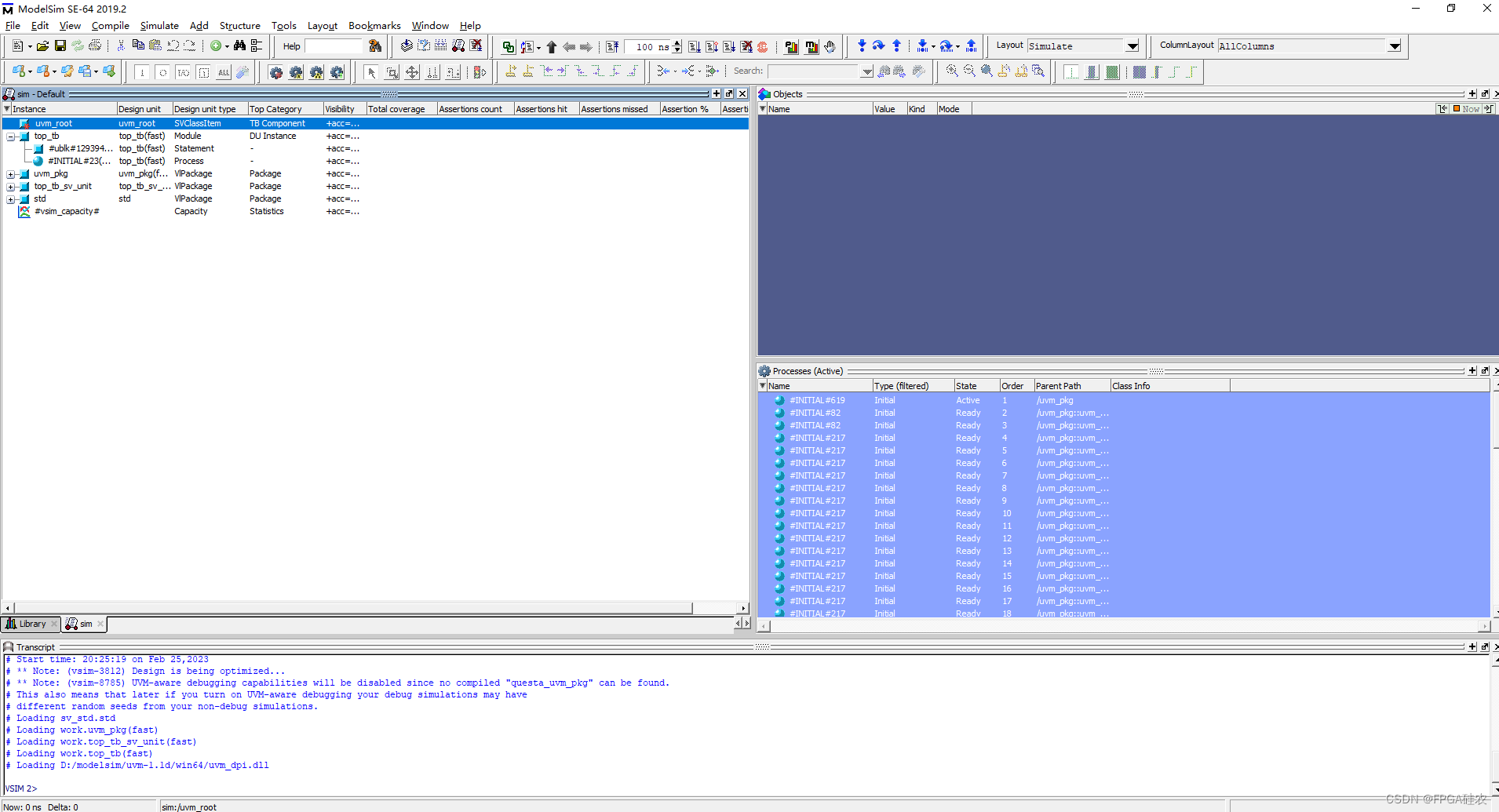

双击run.bat,跳出如下界面

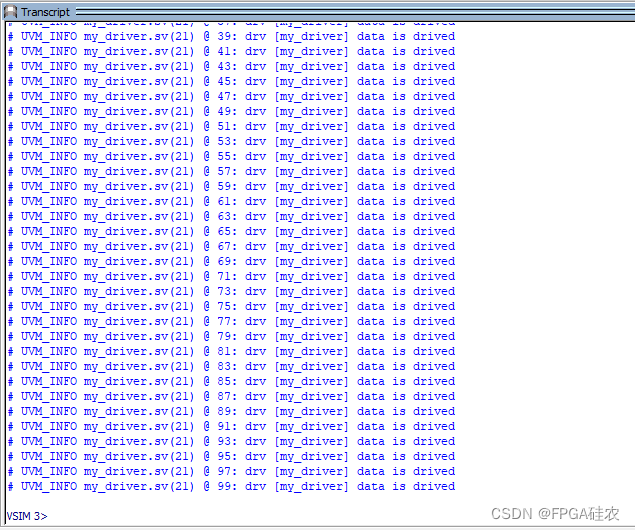

执行命令run 100,得到如下输出

表明driver正常工作。

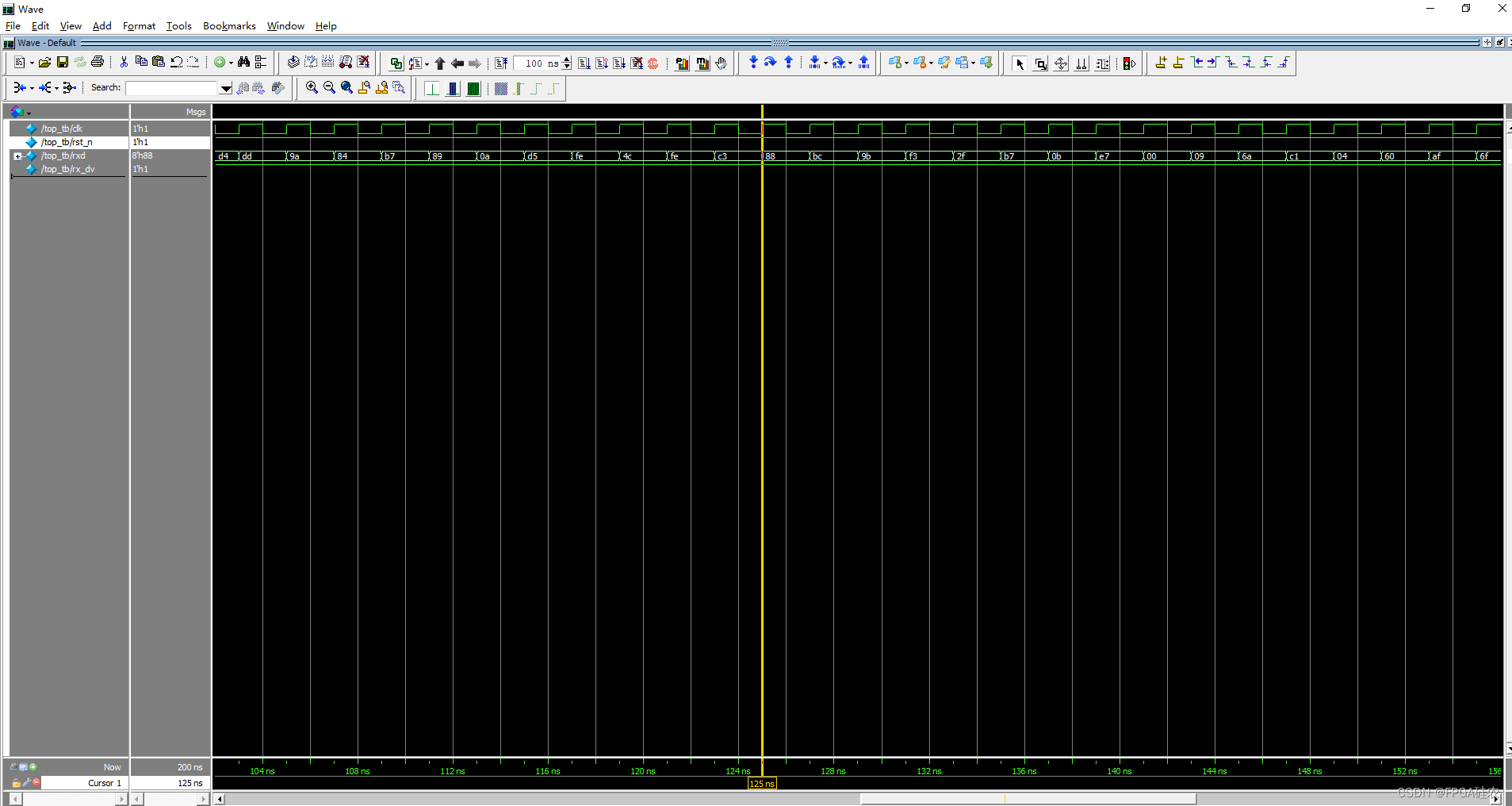

执行add wave *,可以观察到如下所示的波形: