音乐播放器蜂鸣器ROM存储歌曲verilog,代码/视频

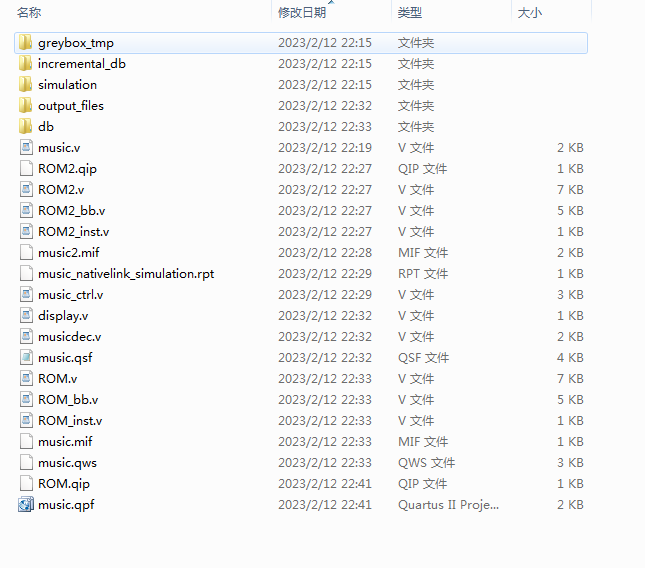

名称:音乐播放器蜂鸣器ROM存储歌曲

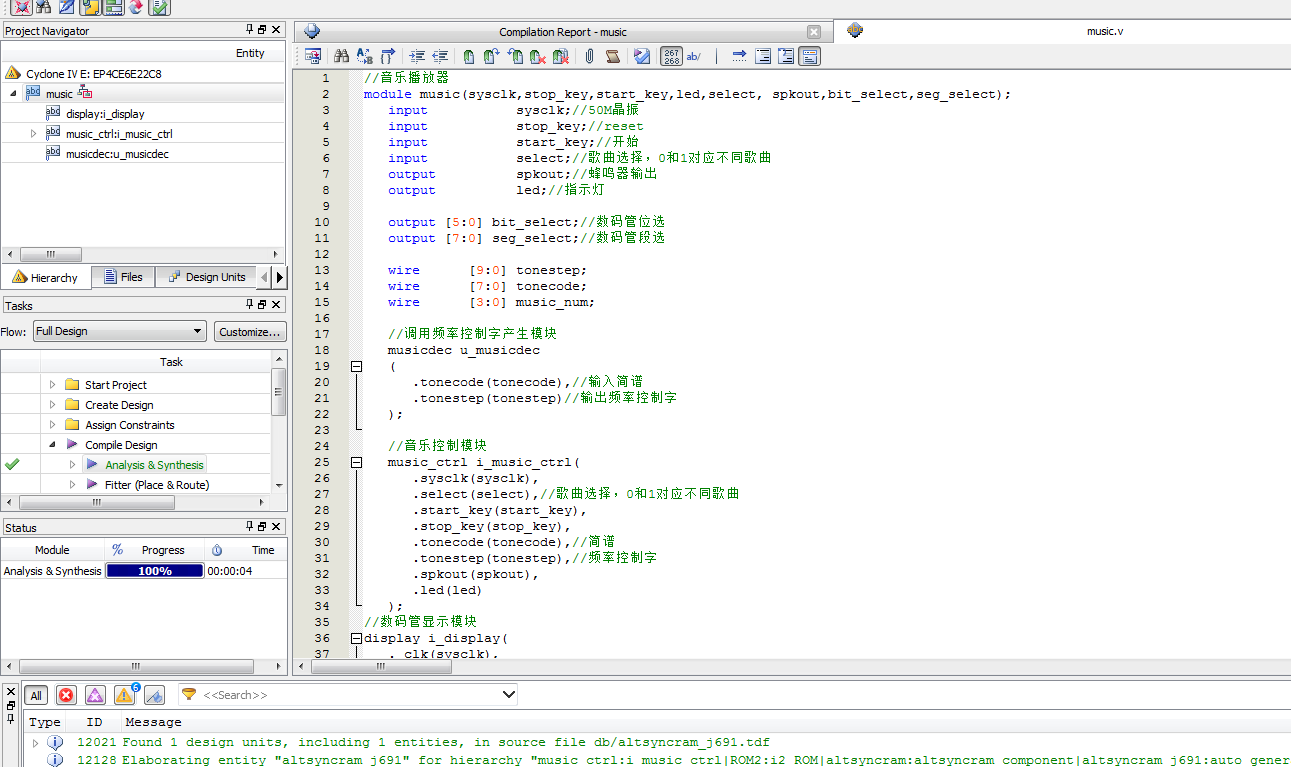

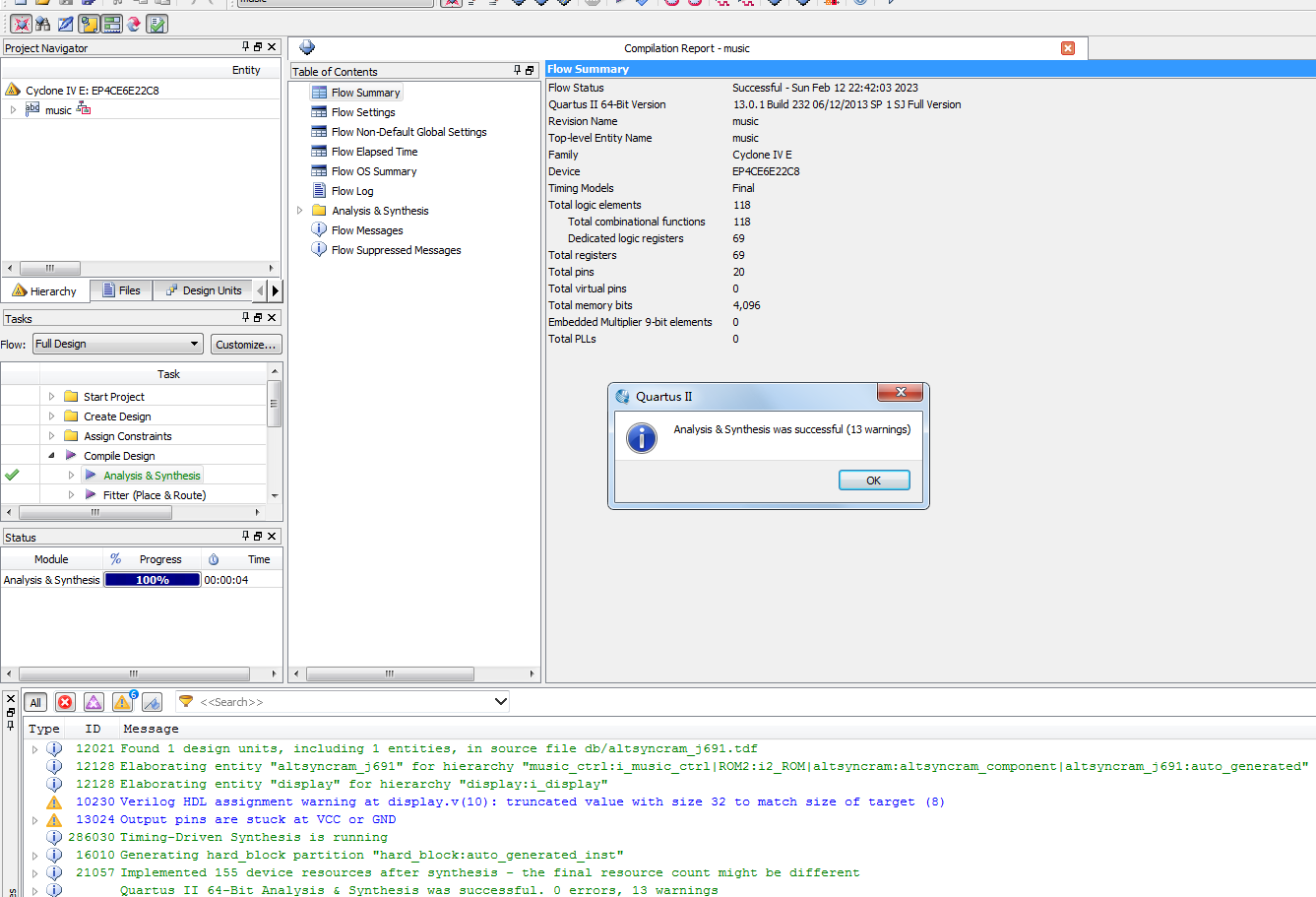

软件:Quartus

语言:Verilog

代码功能:

设计音乐播放器,要求至少包含2首歌曲,使用按键切换歌曲,使用开发板的蜂鸣器播放音乐,使用Quartus内的ROM IP核存储音乐文件,

简谱存储在ROM中,共2首歌曲。

《茉莉花》的简谱存储在ROM中,具体值可以打开music.mif文件查看

《两只老虎》的简谱存储在ROM2中,具体值可以打开music2.mif文件查看

mif文件说明:

8表示简谱1

9表示简谱2

10表示简谱3

以此类推

每个简谱对应4个相同的值

演示视频:音乐播放器蜂鸣器ROM存储歌曲Verilog_Verilog/VHDL资源下载

代码下载:音乐播放器蜂鸣器ROM存储歌曲Verilog_Verilog/VHDL资源下载名称:音乐播放器蜂鸣器ROM存储歌曲(代码在文末付费下载)软件:Quartus语言:Verilog代码功能: 设计音乐播放器,要求至少包含2首歌曲,使用按键切换歌曲,使用开发板的蜂鸣器播放音乐,使用Quartus内的ROM IP核存储音乐文件,简谱存储在ROM中,共2首歌曲。 《茉莉花》的简谱存储在ROM中,具体值可以打开music.mif文件查看 《两只老虎》的简谱存![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=194

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=194

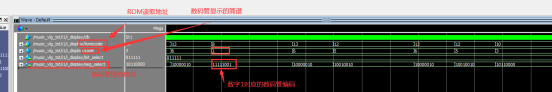

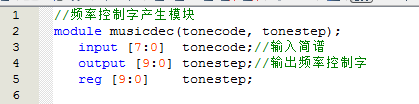

部分代码展示

//播放器控制模块 module music_ctrl(sysclk,stop_key,select,start_key,tonecode,tonestep,led,spkout);input sysclk;//50M晶振 input stop_key;//reset input select;//歌曲选择,0和1对应不同歌曲 input start_key;//开始 input [9:0] tonestep;output [7:0] tonecode; output led;//指示灯 output spkout;//蜂鸣器输出reg spkout=0;reg [10:0] addr='d0;//分频控制字--addr[21:0]reg [24:0] divclk_counter='d0;reg musicclk=0;wire [9:0] step;reg [7:0] tonecode='d0;wire [9:0] tonestep;reg [7:0] codeaddr1='d0; reg [7:0] codeaddr2='d0;wire [7:0] ROM_data1; wire [7:0] ROM_data2; //ROM(歌曲茉莉花) ROM i1_ROM( .address(codeaddr1), .clock(musicclk), .q(ROM_data1) ); //ROM(歌曲两只老虎) ROM2 i2_ROM( .address(codeaddr2), .clock(musicclk), .q(ROM_data2) ); reg music_select=1'd0; assign led=music_select; always@(posedge sysclk or negedge stop_key or negedge start_key) if(!stop_key) music_select<=0;//停止 else if(!start_key) music_select<=1;//开始assign step = tonestep;always @(posedge sysclk) begin addr <= addr + step;//step是根据音乐文件产生的频率控制字,不同step产生不同频率的spkoutendalways @(posedge sysclk) beginif (divclk_counter == 179)//50M/(1799999*2)=分频到13.9Hz---仿真将1799999改小为179beginmusicclk <= (~musicclk);//musicclk=13.9Hzdivclk_counter <= 0;endelsedivclk_counter <= divclk_counter + 1;end always @(posedge sysclk) if(music_select==0)begin spkout<=1'b1;//0时蜂鸣器拉高,不唱 end else begin spkout<=addr[10];//addr的最高位就是输出蜂鸣器的频率--仿真将addr[21]改成addr[10] endalways @(posedge musicclk or negedge stop_key)begin if(!stop_key) codeaddr1 <= 0;//停止 else if(select==0)begin//歌曲1if (music_select)begintonecode <= ROM_data1;//播放歌曲if (codeaddr1 == 255)codeaddr1 <= 0;//播放完后循环elsecodeaddr1 <= codeaddr1 + 1;end end

设计文档:

1. 工程文件

2. 程序文件

ROM文件

Mif文件

3. 程序编译

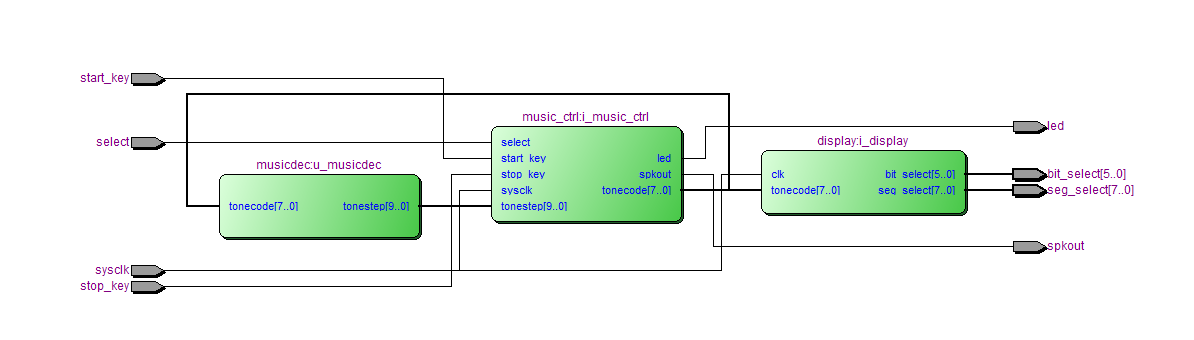

4. RTL图

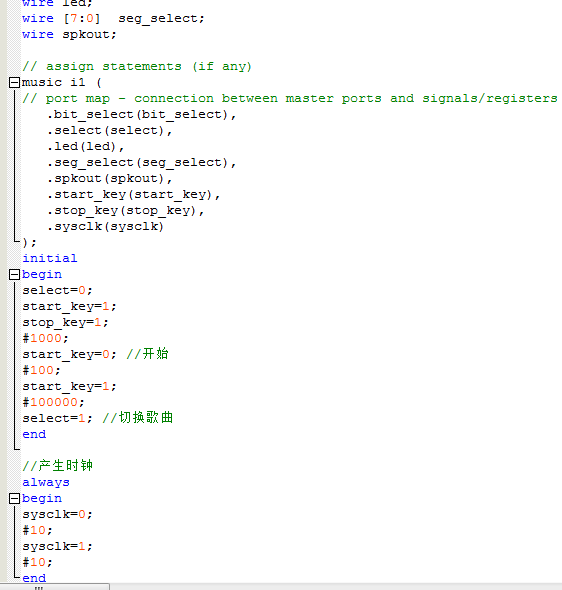

5. Testbench

6. 仿真图

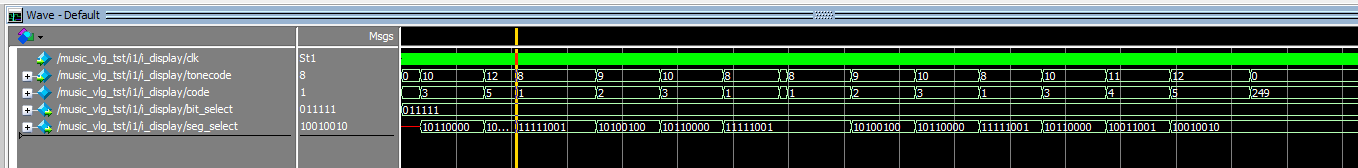

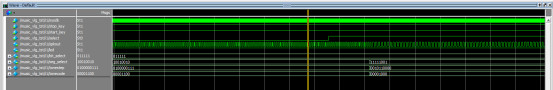

整体仿真图

音乐控制模块

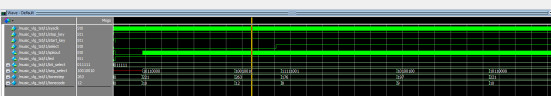

频率控制模块

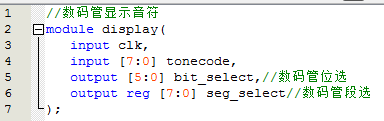

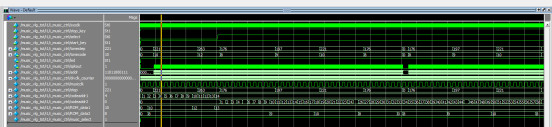

数码管显示模块