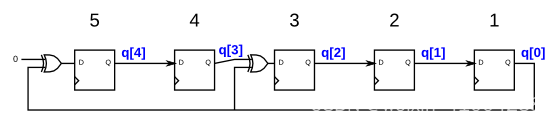

HDLbits: Lfsr5

我的错误写法,半成品,完全错误:

module top_module(input clk,input reset, // Active-high synchronous reset to 5'h1output [4:0] q

); dff dff_1(clk, 0 ^ q[0],q[4]);dff dff_2(clk, q[4] ,q[3]);dff dff_3(clk, q[3] ^ q[0] ,q[2]);dff dff_4(clk, q[2] ,q[1]);dff dff_5(clk, q[1] ,q[0]);always@(posedge clk)if(reset)q <= 1;elseq <= q;

endmodulemodule dff(input clk, input d, output Q);always@(posedge clk)Q <= d;

endmodule参考网友的写法:

module top_module(input clk,input reset, // Active-high synchronous reset to 5'h1output [4:0] q

); always@(posedge clk)if(reset)q <= 5'h1;elseq <= {0 ^ q[0],q[4],q[3]^q[0],q[2],q[1]};

endmodule官方的写法:感觉像第一个always是一个组合逻辑块(阻塞赋值,执行有先后顺序),第二个always是时序逻辑块。

其中,q_next[4] = q[0];应该是q_next[4] = q[0] ^ 0; 因为值不变省略了。

另外q_next = q[4:1]; 应该是q_next ={q[0],q[4:1]};

module top_module(input clk,input reset,output reg [4:0] q);reg [4:0] q_next; // q_next is not a register// Convenience: Create a combinational block of logic that computes// what the next value should be. For shorter code, I first shift// all of the values and then override the two bit positions that have taps.// A logic synthesizer creates a circuit that behaves as if the code were// executed sequentially, so later assignments override earlier ones.// Combinational always block: Use blocking assignments.always @(*) beginq_next = q[4:1]; // Shift all the bits. This is incorrect for q_next[4] and q_next[2]q_next[4] = q[0]; // Give q_next[4] and q_next[2] their correct assignmentsq_next[2] = q[3] ^ q[0];end// This is just a set of DFFs. I chose to compute the connections between the// DFFs above in its own combinational always block, but you can combine them if you wish.// You'll get the same circuit either way.// Edge-triggered always block: Use non-blocking assignments.always @(posedge clk) beginif (reset)q <= 5'h1;elseq <= q_next;endendmodule