北邮22级信通院数电:Verilog-FPGA(3)实验“跑通第一个例程”modelsim仿真及遇到的问题汇总(持续更新中)

北邮22信通一枚~

跟随课程进度更新北邮信通院数字系统设计的笔记、代码和文章

持续关注作者 迎接数电实验学习~

获取更多文章,请访问专栏:

北邮22级信通院数电实验_青山如墨雨如画的博客-CSDN博客

注意:本篇文章所有绝对路径的展示都来自上一篇博客

北邮22级信通院数电:Verilog-FPGA(2)modelsim北邮信通专属下载、破解教程_青山如墨雨如画的博客-CSDN博客

目录

操作步骤及批注

步骤一

步骤二

*批注

*批注

*批注

*批注

步骤三

步骤四

*批注:

*几种常见问题

*1.Unable to checkout a license.

*问题描述

*解决方法

*2.objects和process中都没有东西

*问题描述

*解决方法

*情况1:

*解决办法:

*情况2:

*解决方案:

接操作步骤与批注

步骤五

*批注

步骤六

步骤七

步骤八

步骤九

说明:本篇博客一共有两套目录,不带“*”的一套目录是正常流程,带“*”的一套目录是小编自己的批注和遇到的问题及解决方案~

如果读者没有根据上一篇博客进行配置, 请读者按照自己的实际路径自行配置。

操作步骤及批注

步骤一

选择菜单栏Assignments→Settings 或 工具栏中Settings按钮,进入设置界面。

步骤二

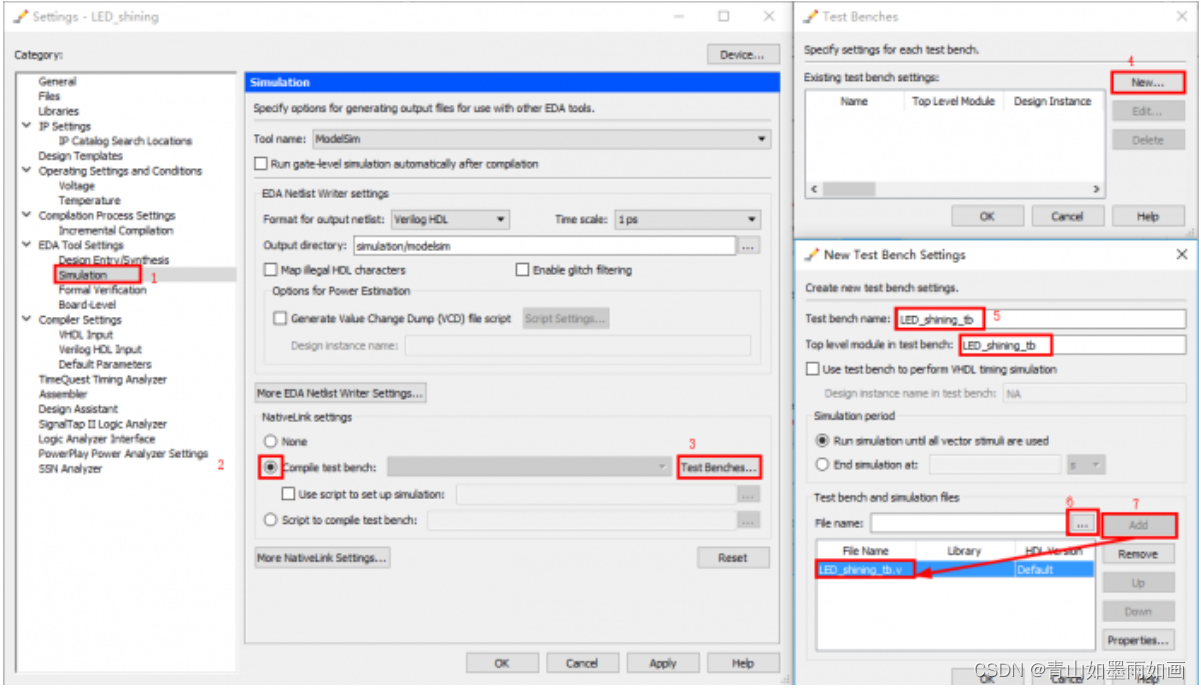

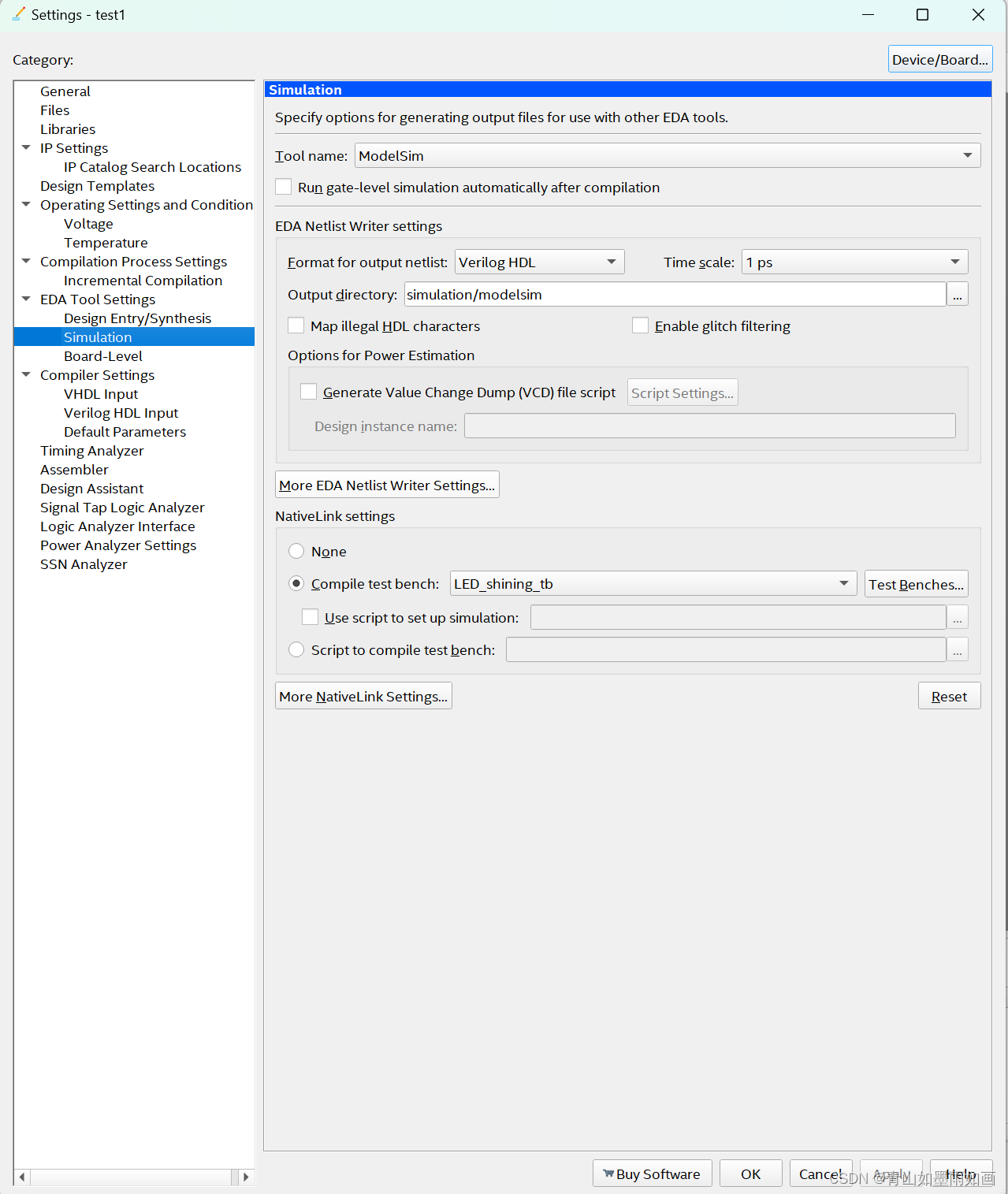

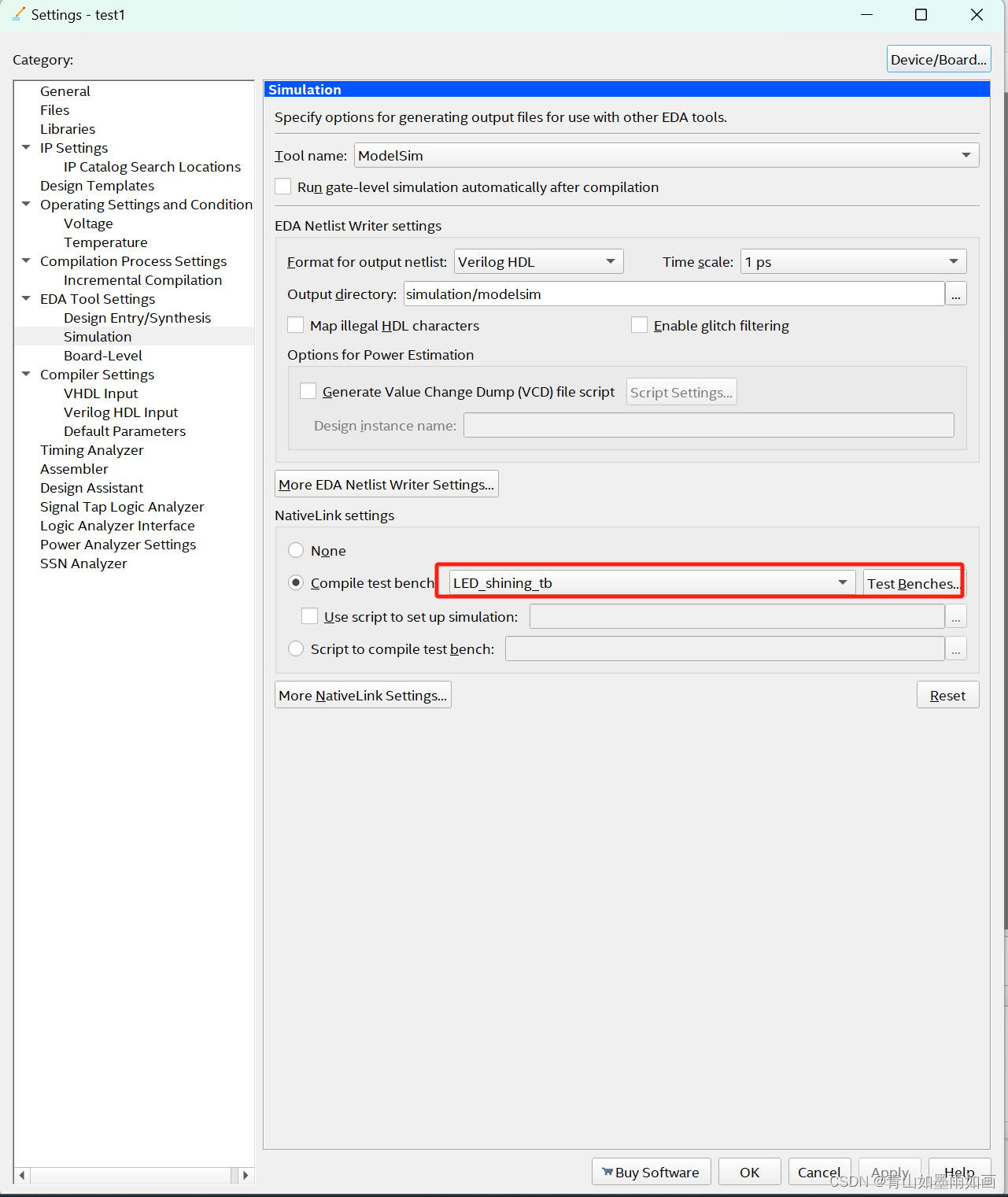

选择菜单栏Simulation选项,单选Compile test bench,点击Test Benches,在弹出的对话框中点击New,填写Test bench name,按照目录添加测试文件,如下图标识顺序,最后点击OK回到设计界面。

*批注

Test Bench Name必须和测试文件名一致。比如第二个.v文件的名字是LED_shining_tb,那么这个 Test Bench Name就必须是LED_shining_tb。

*批注

Add Files的时候,找到你的LED_shining_tb.v文件所在的位置。一般在D:\intelFPGA_lite\22.1std\quartus\bin64中,看你LED_shining_tb.v原先存放在哪里了。

*批注

一定要点“Add”!!!之后一直点“OK”。

*批注

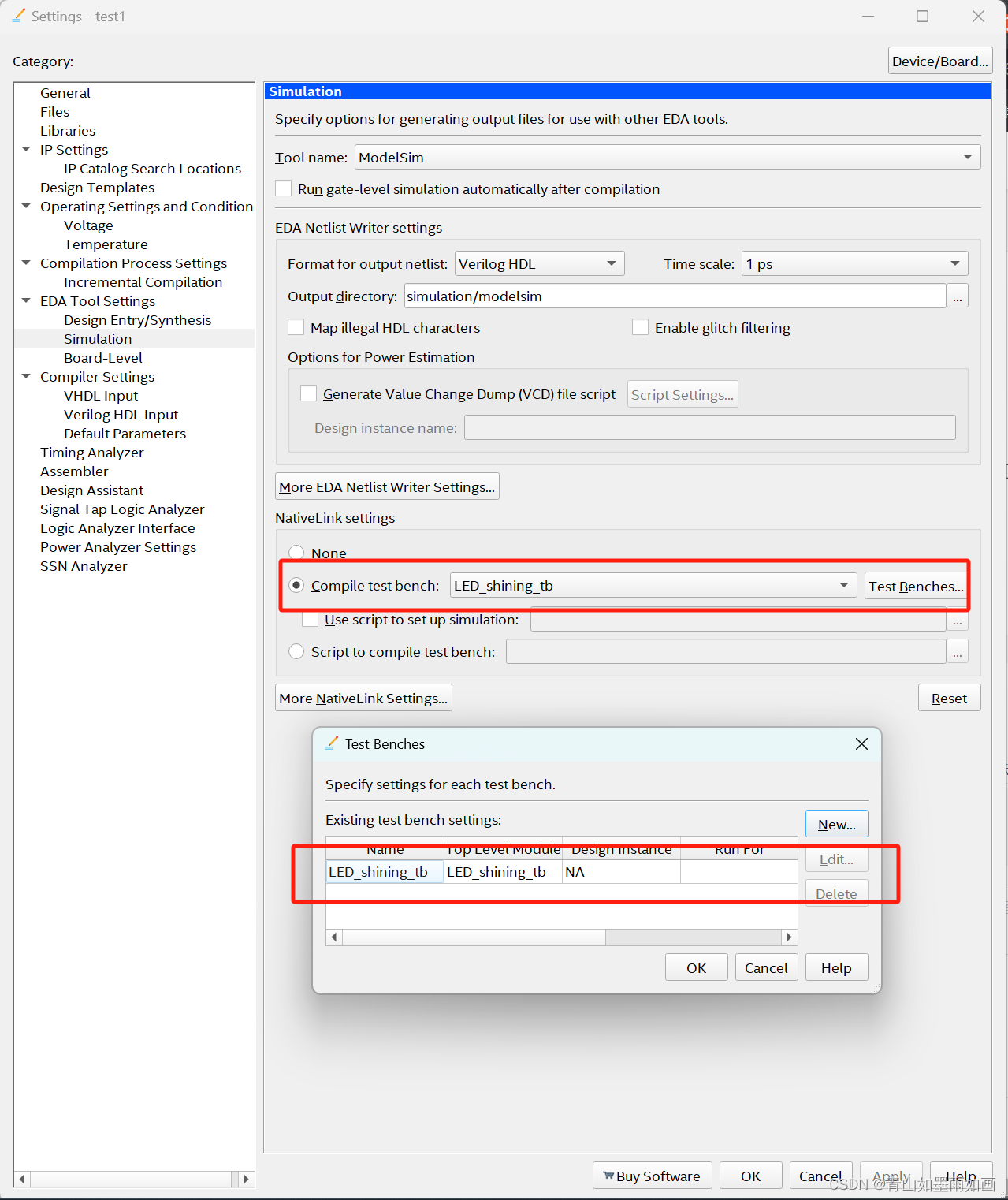

最后在“compile test bench”后面你就可以看到这样的效果:

步骤三

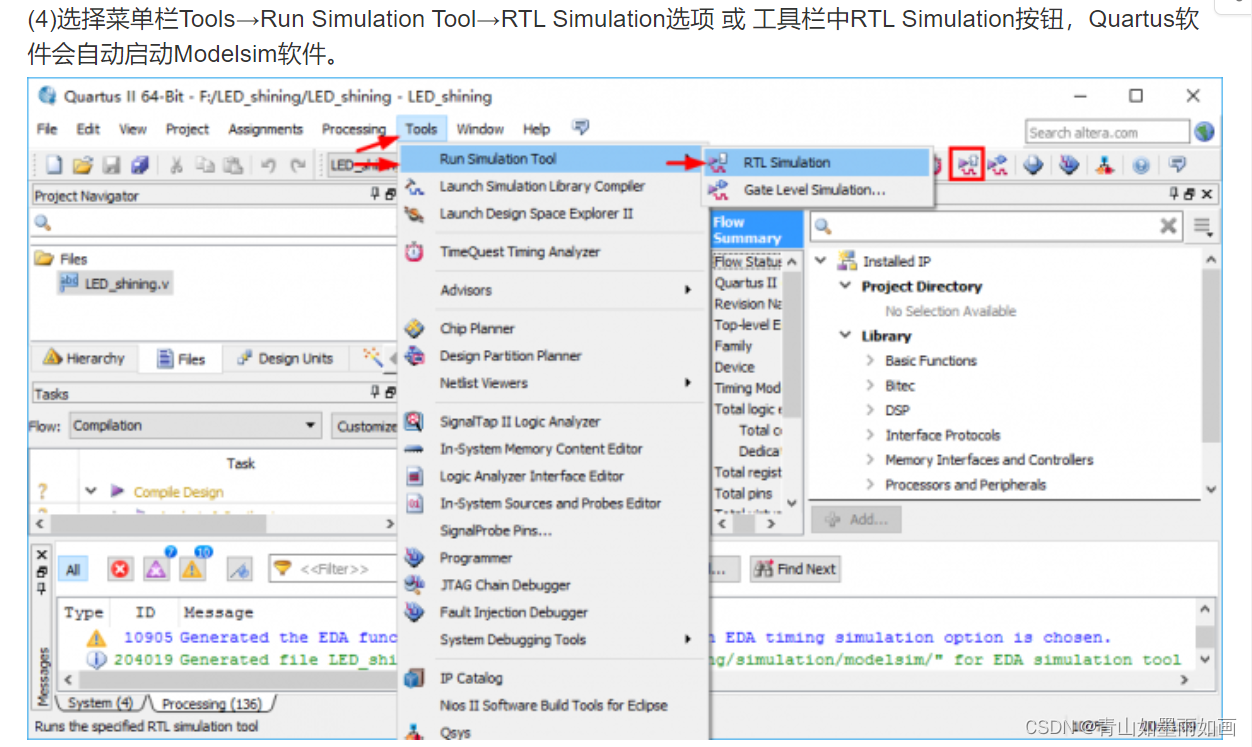

选择菜单栏Tools→Run Simulation Tool→RTL Simulation选项 或 工具栏中RTL Simulation按钮,Quartus软件会自动启动Modelsim软件。

步骤四

Modelsim软件启动后自动完成代码编译,界面如下图。

*批注:

*几种常见问题

*1.Unable to checkout a license.

*问题描述

modelsim显示

Unable to checkout a license. Make sure your license file environment variable (e.g, LM LICENSE FILE)is set correctly and then run lmutil lmdiag' to diagnose the problem.

有些同学按照上面的步骤走完之后,运行 RTL simulation会跳出这个界面,仿真无法继续进行。

*解决方法

重启。

好几个同学遇到了这个问题,都按照这个方法解决了。亲测有效。

*2.objects和process中都没有东西

*问题描述

运行之后,transcript中有很多生成的语句,但是objects和process中都没有东西。这个问题很复杂,目前研究过的几种可能情况如下:

*解决方法

simulation如果运行成功,transcript最后一行应该为#run -all。如果最后一行不是这个,在transcript中向上翻找。

*情况1:

如果transcript中有红色字的,注意看报错信息

*解决办法:

1.检查各种名字

检查各种名字,看是不是都一致;各种名字包括:LED_shining_tb模块名;LED_shining_tb文件名;LED_shining模块名;LED_shining_uut模块名;LED_shinig文件名;工程名;在assignments->settings->simulation->compile test bench中添加的文件名和新建的文件名都应该是LED_shining_tb

2.检查modelsim安装路径和引用路径是否完全一致

注意:本篇文章所有绝对路径的展示都来自上一篇博客,如果读者没有根据上一篇博客进行配置,请自行找到modelsim安装包的win64文件夹的绝对位置。

注意:引用路径能且只能填到win64文件夹!!!(绝对路径:D:/modeltech64_2020.4/win64/)

注意:win64后面必须加“/”!!!

3.检查所有和仿真相关的编译器是不是都是modelsim

具体包括:

*情况2:

如果transcript里没有红色字且没有报错信息,modelsim能运行但object和process全为空

*解决方案:

assignments->settings->simulation应该没配或者没配对。

接操作步骤与批注

步骤五

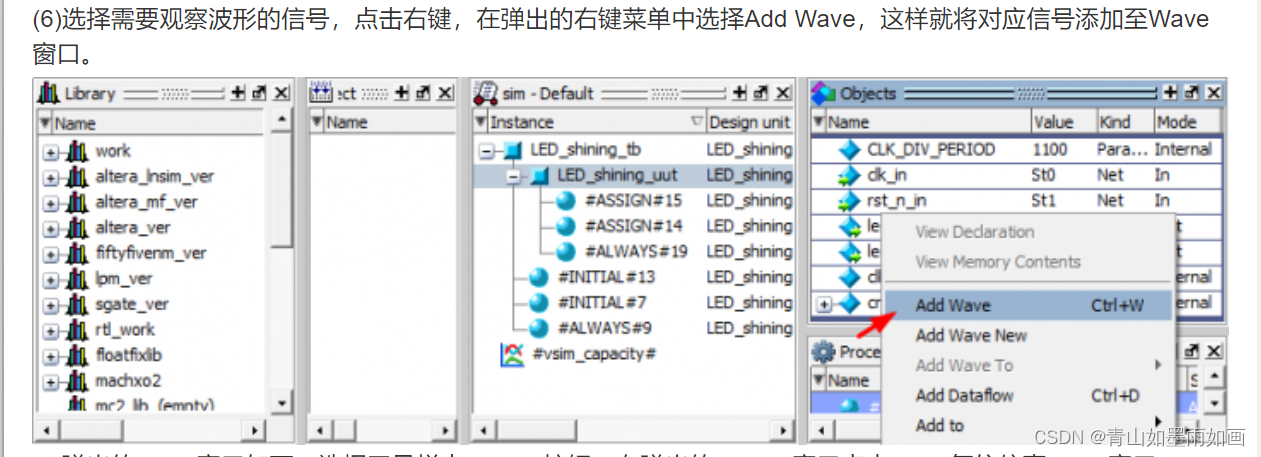

选择需要观察波形的信号,点击右键,在弹出的右键菜单中选择Add Wave,这样就将对应信号添加至Wave窗口。

*批注

选中之后Ctrl+W也行。

步骤六

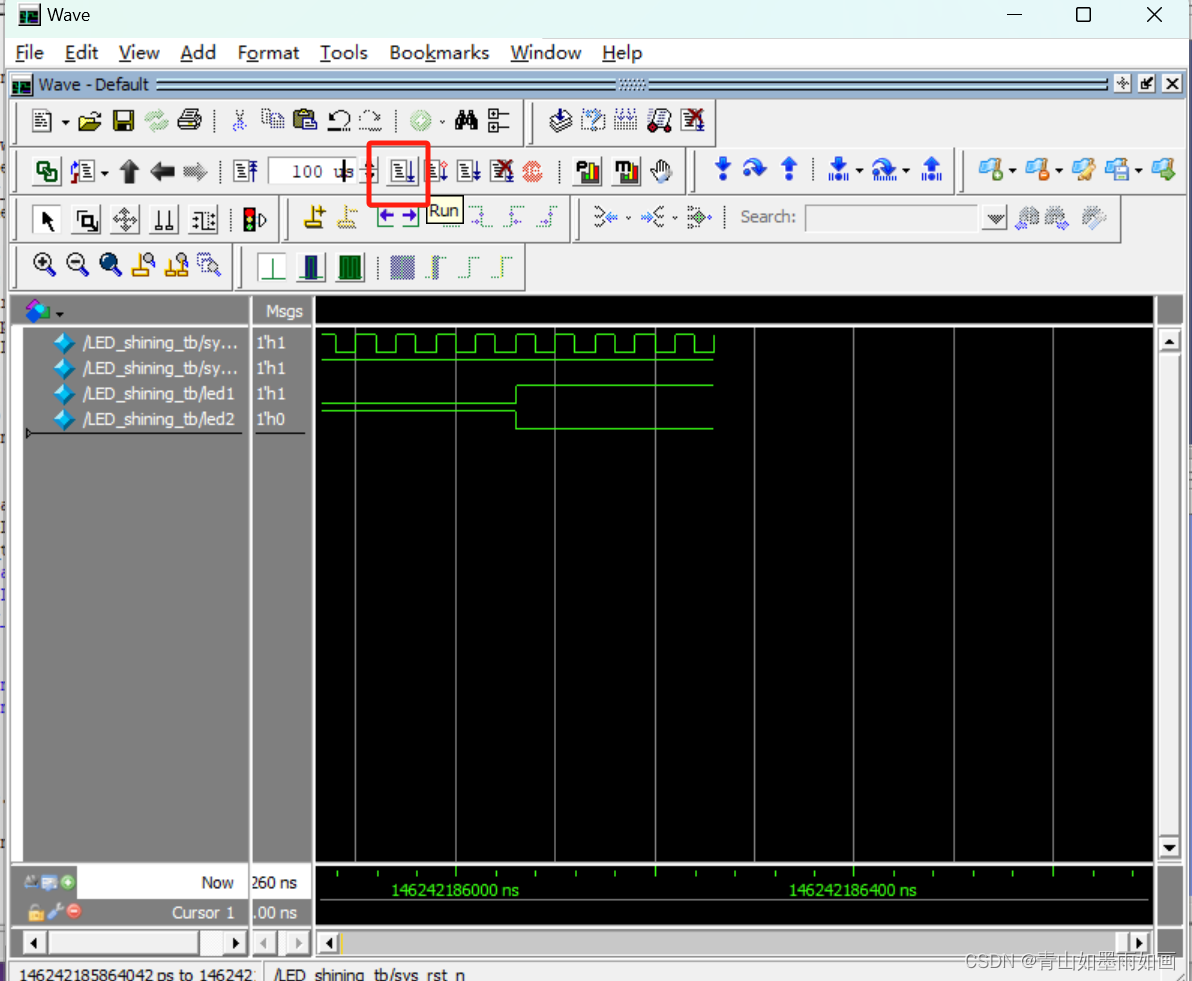

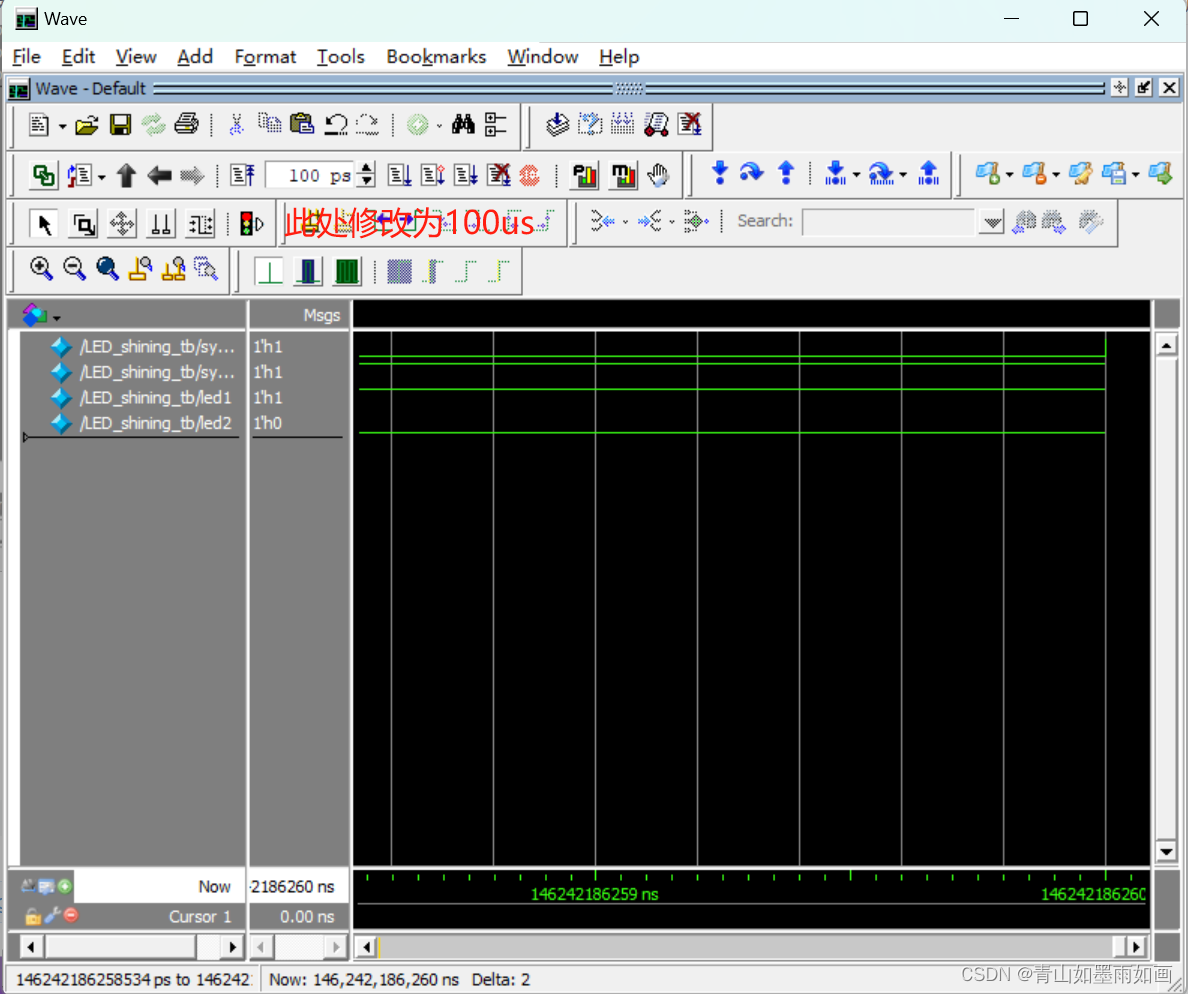

在wave窗口点击stop

步骤七

步骤八

按1、2顺序执行

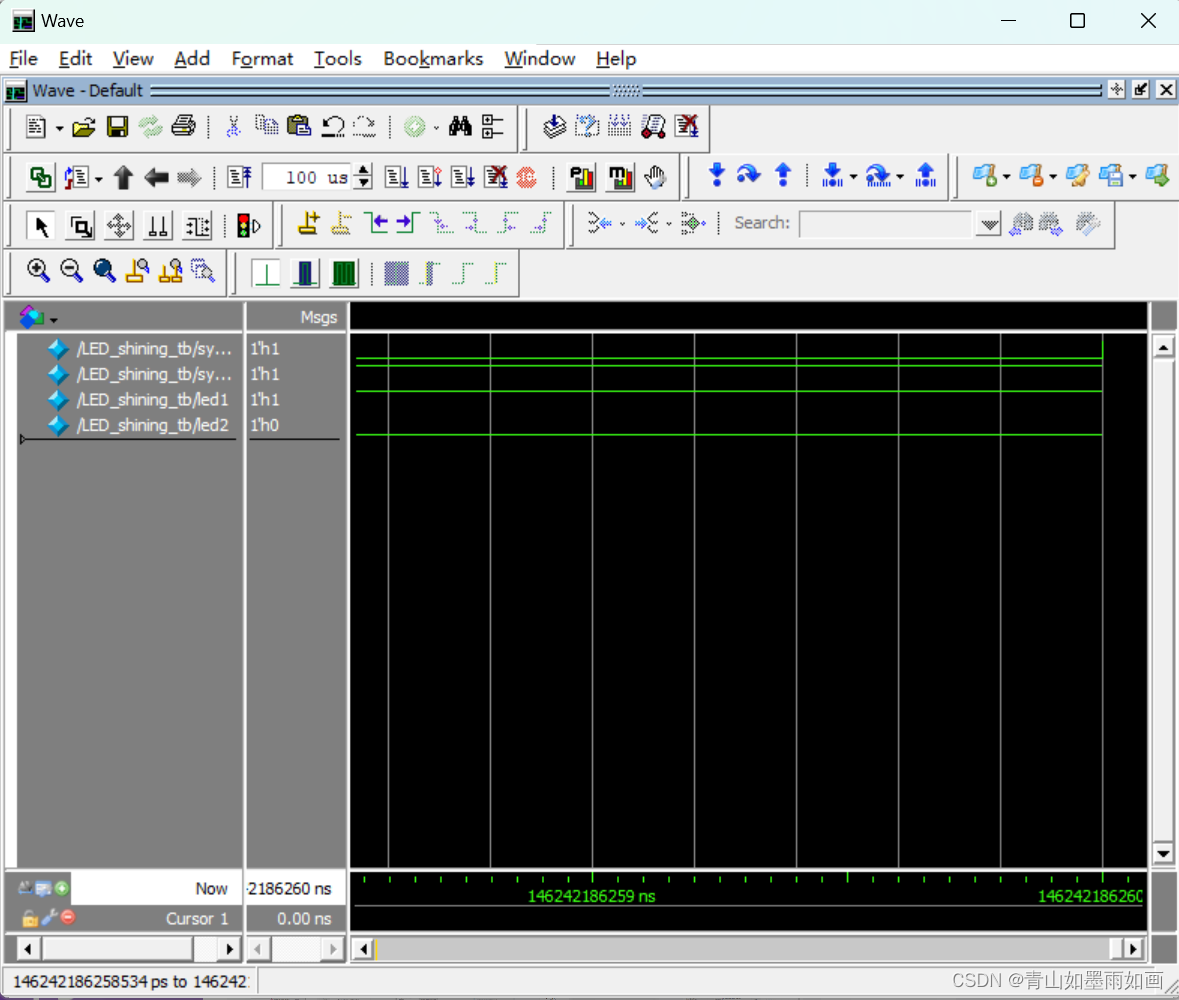

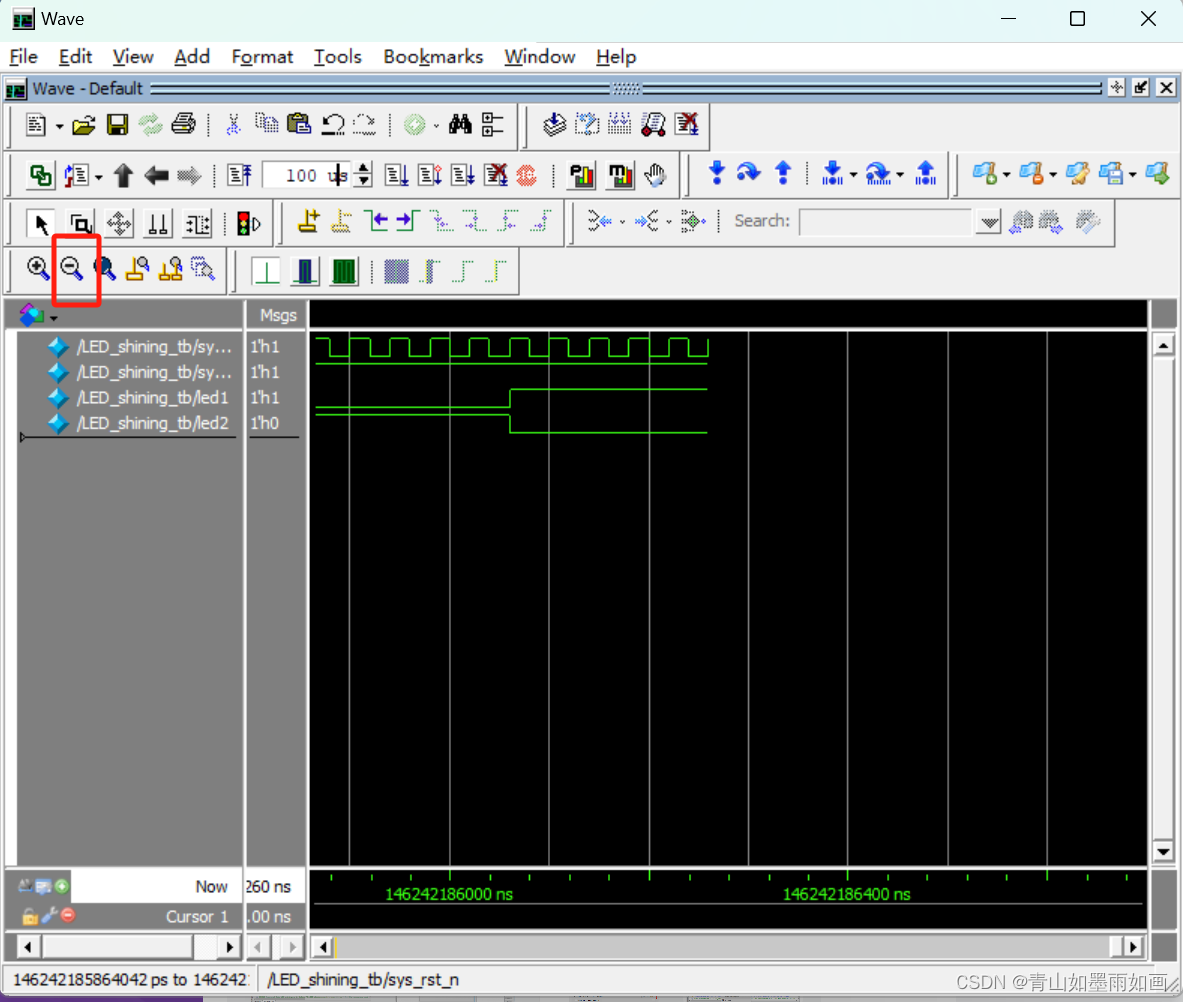

步骤九

一直点缩小窗口,直到图像正确为止。

也可以继续run。