SPI总线协议

简述

SPI协议是一种芯片与芯片之间的通讯,全称是Serial Peripheral Interface

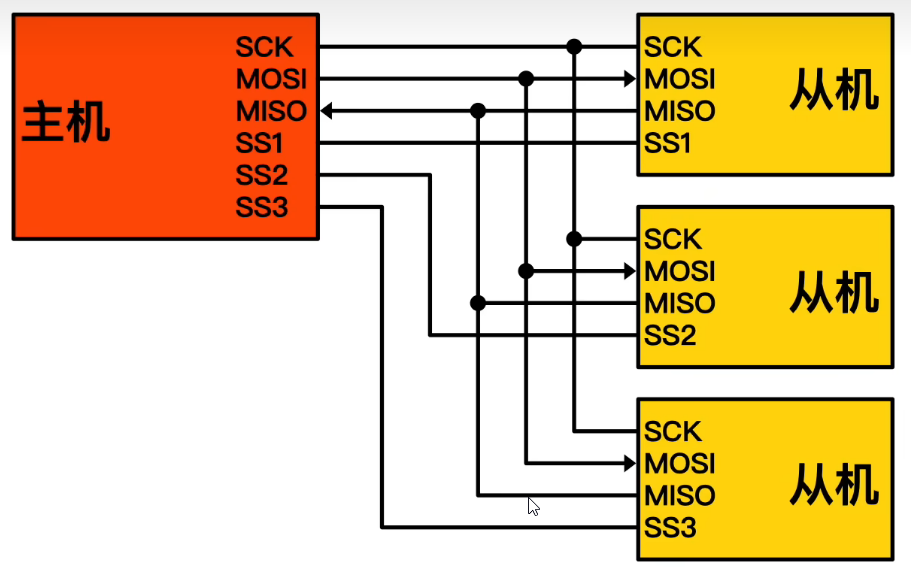

SPI通讯采用一主多从模式,产生时钟的一侧称为主机,另一侧称为从机。只有一个主机(一般来说可以是微控制器/MCU),但是可以有一个或者多个从机

SPI通讯需要4条信号线

1、SS

Slave Select 片选信号,由主机通过给片选信号线高低电平来决定与哪一个从机通信,通常是低电平有效信号。

2、SCK

Serial Clock 串行时钟信号,由主机产生发送给从机;

3、MOSI

Master output slave input 主设备通过MOSI发送数据,而从设备通过这条线接收数据(数据来自主机);

4、MISO

Master input slave output 主机输入,从机输出(数据来自从机);

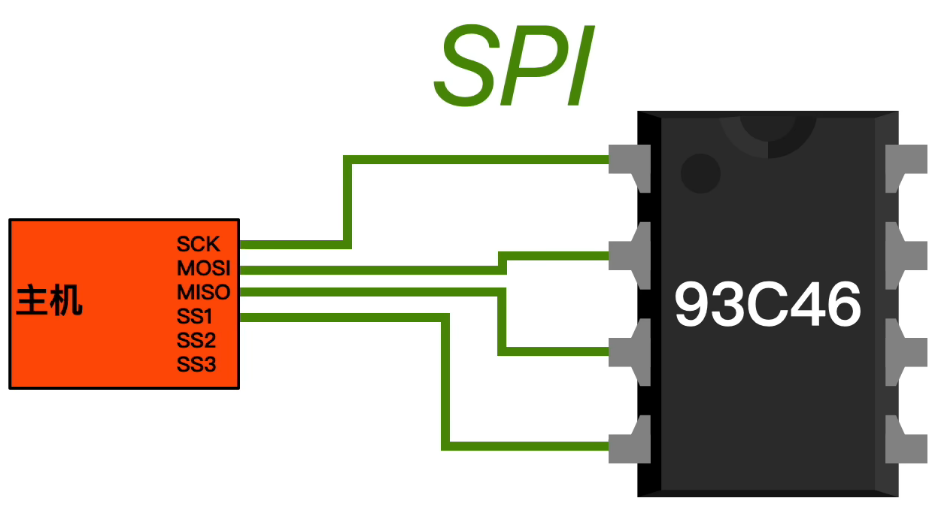

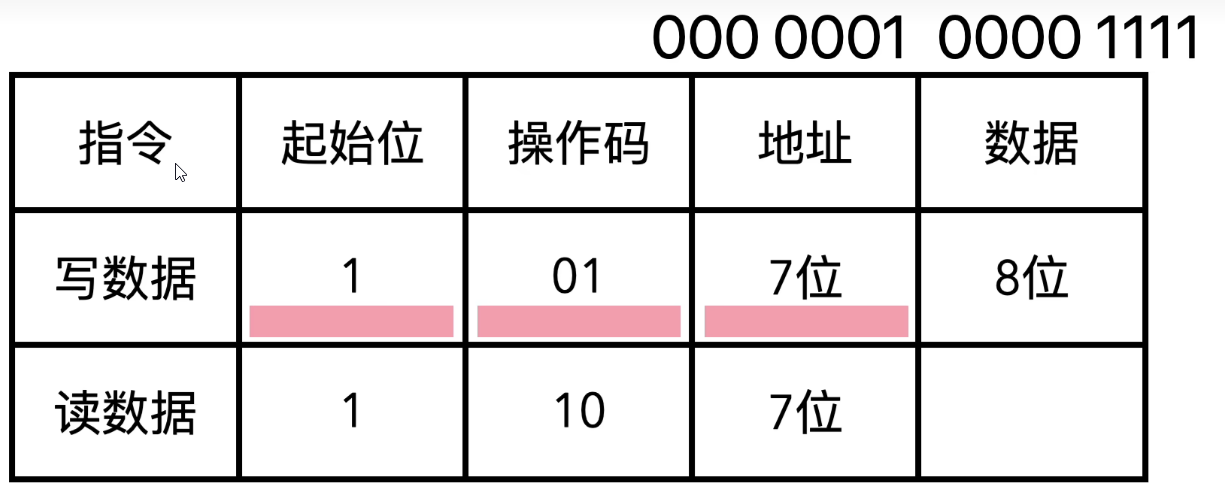

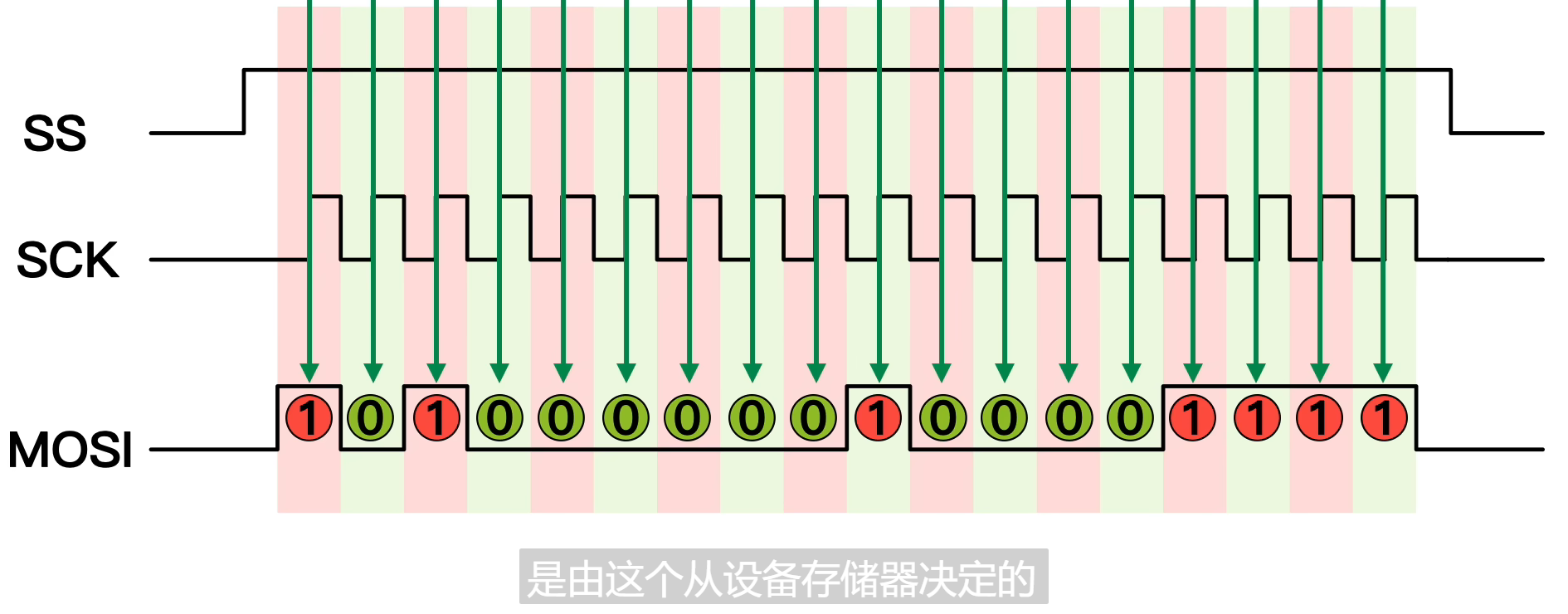

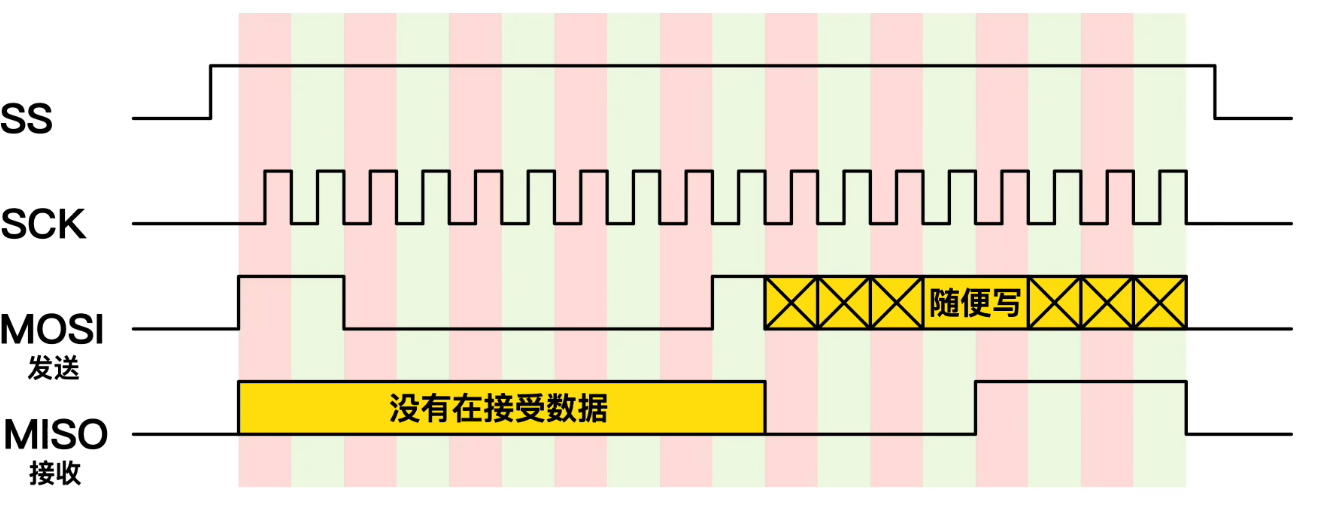

以读取93C46为例

根据数据手册他的SS在高电平有效

给存储器写入数据

从存储器读数据

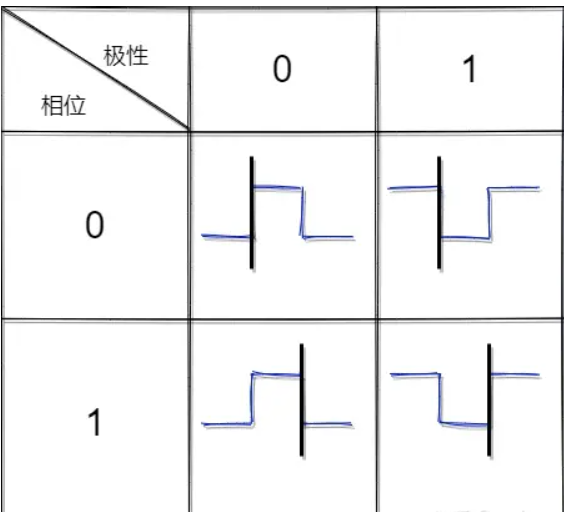

时钟极性 CKP/Clock Polarity

除了配置串行时钟速率(频率)外,SPI主设备还需要配置时钟极性。

根据硬件制造商的命名规则不同,时钟极性通常写为CKP或CPOL。时钟极性和相位共同决定读取数据的方式,比如信号上升沿读取数据还是信号下降沿读取数据;

CKP可以配置为1或0。这意味着您可以根据需要将时钟的默认状态(IDLE)设置为高或低。极性反转可以通过简单的逻辑逆变器实现。您必须参考设备的数据手册才能正确设置CKP和CKE。

CKP = 0:时钟空闲IDLE为低电平0;CKP = 1:时钟空闲IDLE为高电平1;

时钟相位 CKE /Clock Phase (Edge)

除配置串行时钟速率和极性外,SPI主设备还应配置时钟相位(或边沿)。根据硬件制造商的不同,时钟相位通常写为CKE或CPHA;

顾名思义,时钟相位/边沿,也就是采集数据时是在时钟信号的具体相位或者边沿;

CKE = 0:在时钟信号SCK的第一个跳变沿采样;CKE = 1:在时钟信号SCK的第二个跳变沿采样;

时钟配置总结

综上几种情况,下图总结了所有时钟配置组合,并突出显示了实际采样数据的时刻;

其中黑色线为采样数据的时刻;

蓝色线为SCK时钟信号;

具体如下图所示;