基于IMX6ULLmini的linux裸机开发系列九:时钟控制模块

时钟控制模块

核心

4个层次配置芯片时钟

-

晶振时钟

-

PLL与PFD时钟

-

PLL选择时钟

-

根时钟/外设时钟

系统时钟来源

-

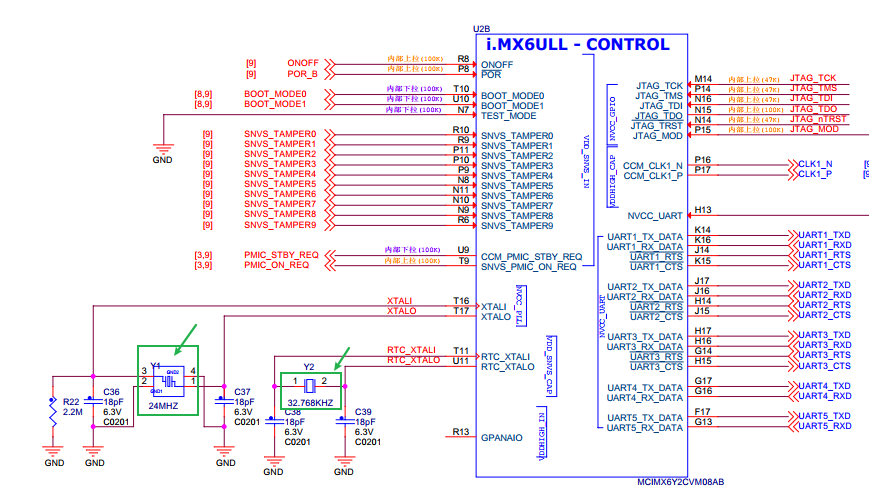

RTC时钟源:32.768KHz

-

系统时钟:24MHz,作为芯片的主晶振使用

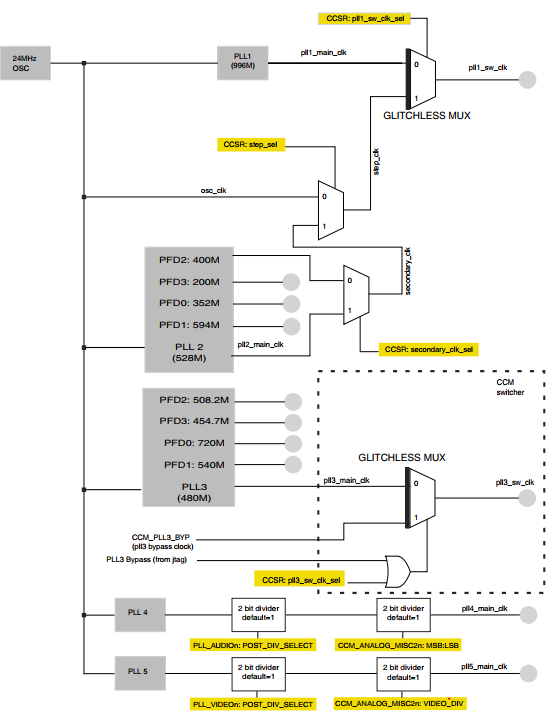

PLL和PFD倍频时钟

7路锁相环电路(每个锁相环电路都可以对时钟进行倍频)

-

ARM_PLL:驱动 ARM 内核

-

528_PLL:频率固定是528MHZ,倍频参数固定为22,系统总线时钟

-

USB1_PLL:驱动第一个 USB 物理层

-

AUDIO_PLL:驱动音频接口

-

VIDEO_PLL:驱动视频接口

-

ENET_PLL:驱动外部以太网接口

-

USB2_PLL:驱动第二个 USB 物理层

-

10.3.1 Centralized components of clock management system

18.6 CCM Memory Map/Register Definition

-

CCM_ANALOG_PLL_XXX

-

设置PPL时钟主频(pll1_main_clk)

-

使能PLL时钟输出

-

-

CCM_ANALOG_PFD_XXX

-

设置PPL下PFD的分频系数

-

PLL选择时钟

对 PLL1 和 PLL3 的输出进行选择、对 PLL4 和 PLL5 进行分频

-

cpu内核时钟来于PLL1时钟。

-

刚上电时,PLL1时钟未初始化,arm内核先使用24M晶振频率,等PLL1时钟稳定输出后,再切换回PLL1时钟。

CCM_CCSR:选择pll1_sw_clk、step_clk时钟源

-

step_clk时钟源设置为24M晶振

-

pll1_main_clk时钟源设置为 step_clk或pll1_main_clk

18.5.1.5.1 Clock Switcher

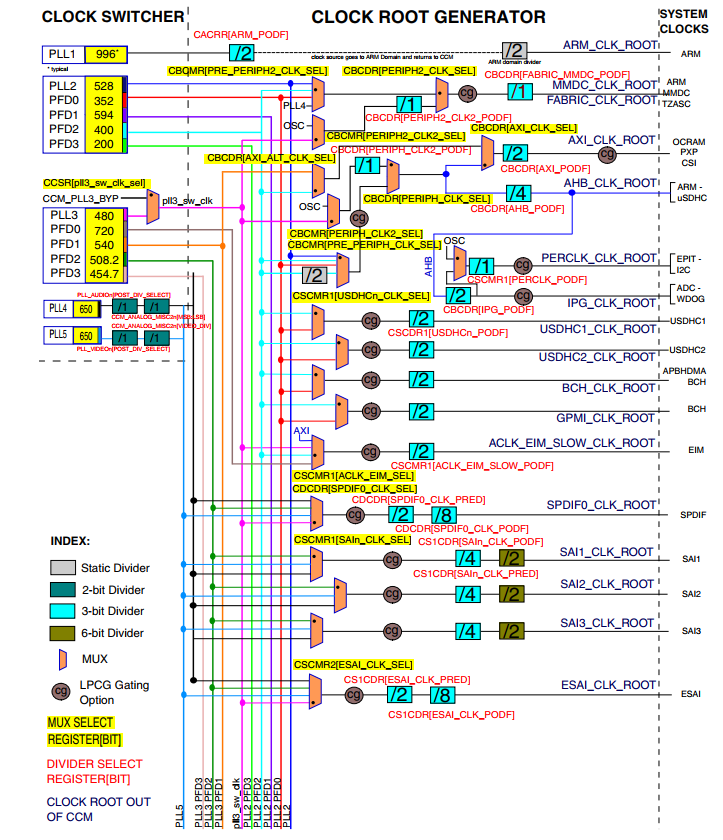

外设时钟

给外设设置时钟源,外设时钟源是可以有多个选择的:

-

梯形图标表示上一级时钟源配置

-

正方形图标表示分频系数

图标旁边标明了相关寄存器

18.3 CCM Clock Tree