FPGA_学习_17_IP核_ROM(无延迟-立即输出)

由于项目中关于厂商提供的温度-偏压曲线数据已经被同事放在ROM表了,我这边可用直接调用。 今天在仿真的时候,发现他的ROM表用的IP核是及时输出的,就是你地址给进去,对应地址的ROM数据就立马输出,没有延迟。 我打开他的IP核配置一看,他用的是Distributed Memory Generator。 我以前用的是Block Memory Generator是要延迟一拍的。所以,我立马进行了Distributed Memory Generator的测试。

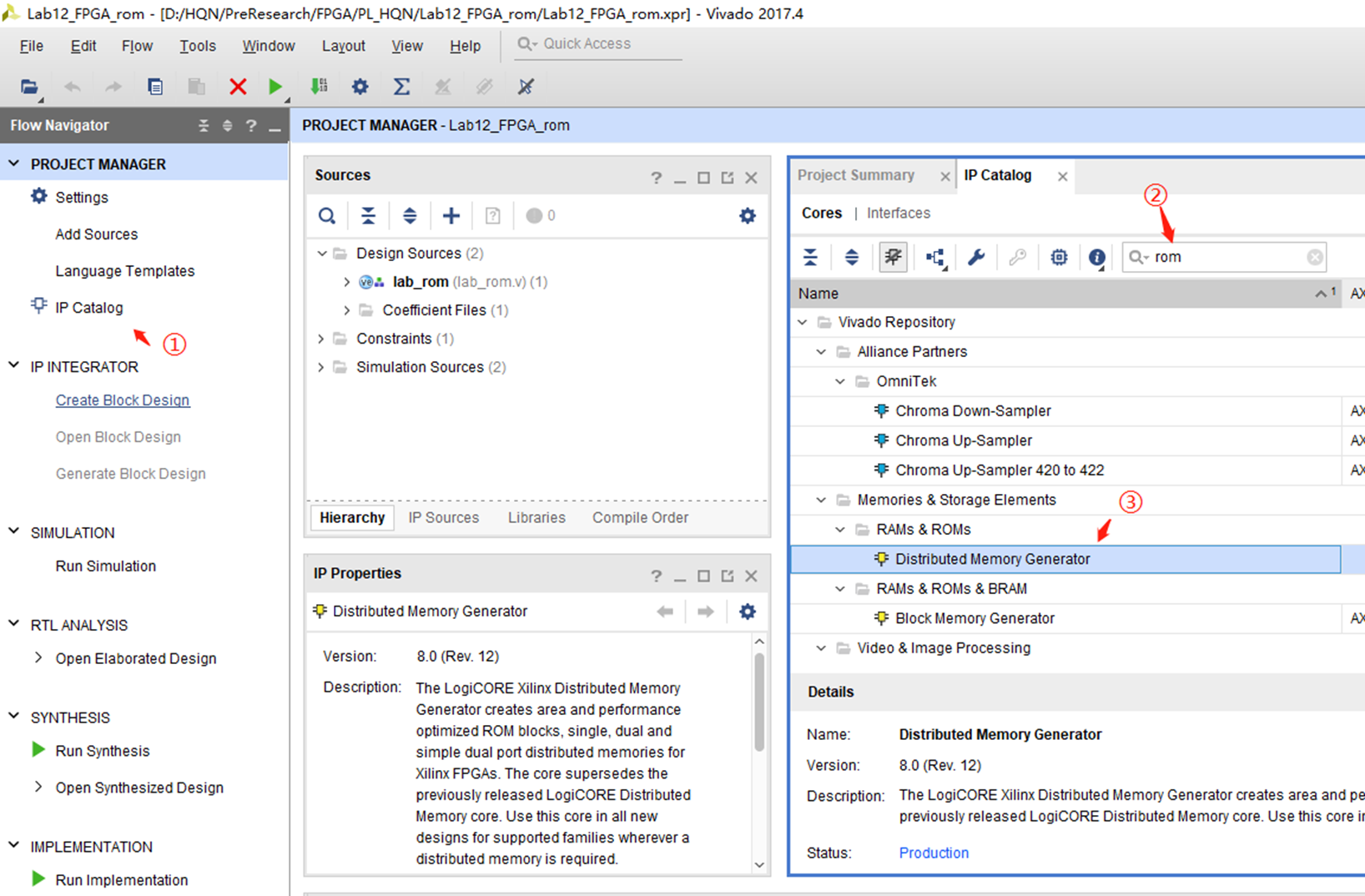

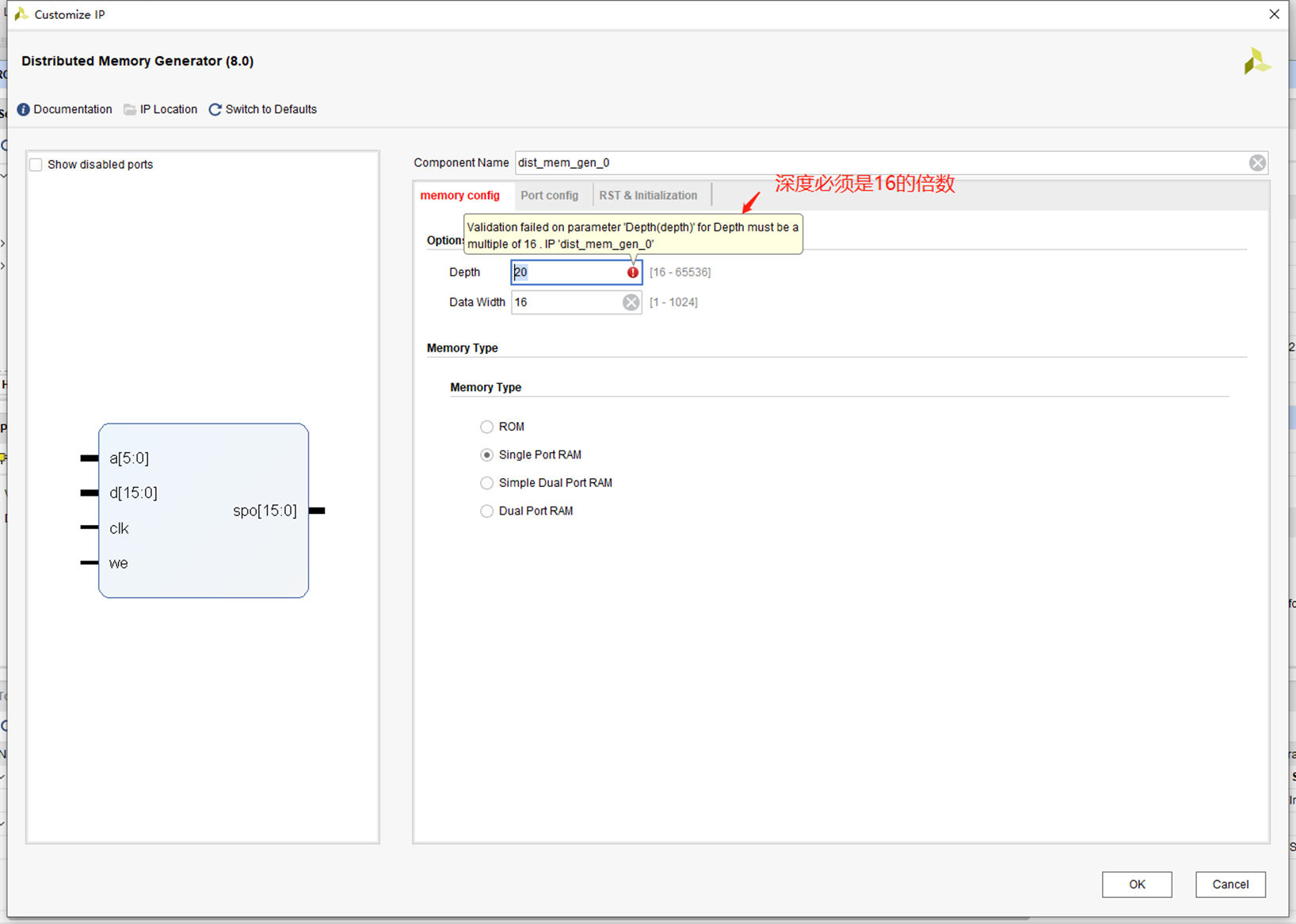

1 ROM IP核配置 (Distributed Memory Generator)

|

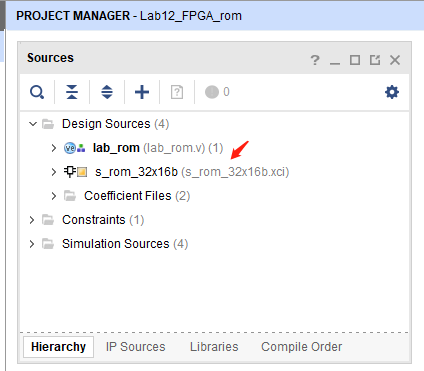

IP核已生成 |

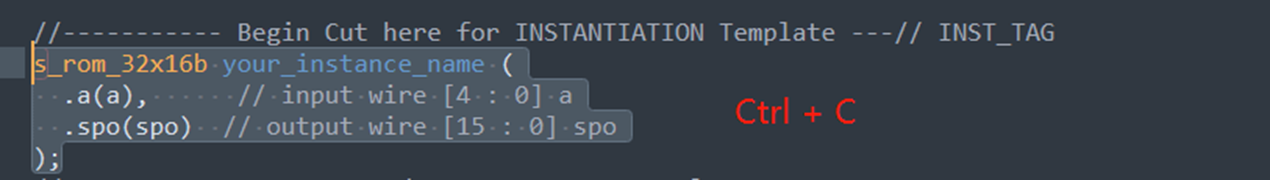

老规矩,查看如何例化 |

2 ModelSim仿真测试

源码

`timescale 1ns / 1psmodule lab_rom(input wire clk,input wire rst_n

);//==================================================================

// Parameter define

//==================================================================

parameter MAX_ADDR = 32 - 1;//==================================================================

// Internal Signals

//==================================================================

(* MARK_DEBUG="true" *) reg [4:0] a;

(* MARK_DEBUG="true" *) wire [15:0] spo;//----------------------------- addra自增 -----------------------------

always @(posedge clk or negedge rst_n) beginif (rst_n == 1'b0) begina <= 'd0; endelse if(a == MAX_ADDR)begina <= 'd0;endelse begina <= a + 1'b1;end

end//----------------------------- s_rom_32x16b例化 -----------------------------

s_rom_32x16b u1_rom_32x16b (.a(a), // input wire [4 : 0] a.spo(spo) // output wire [15 : 0] spo

);

仿真代码

`timescale 1ns/1ps

module tb_lab_rom (); /* this is automatically generated */// clockreg clk;initial beginclk = 1'b0;forever #(10) clk = ~clk;end// asynchronous resetreg rst_n;initial beginrst_n <= 1'b0;#10rst_n <= 1'b1;end// (*NOTE*) replace reset, clock, othersparameter MAX_ADDR = 32 - 1;lab_rom #(.MAX_ADDR(MAX_ADDR)) inst_lab_rom (.clk(clk), .rst_n(rst_n));endmodule

约束文件

create_clock -period 20.000 [get_ports clk]set_property PACKAGE_PIN N18 [get_ports clk]

set_property PACKAGE_PIN T12 [get_ports rst_n]set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports rst_n]

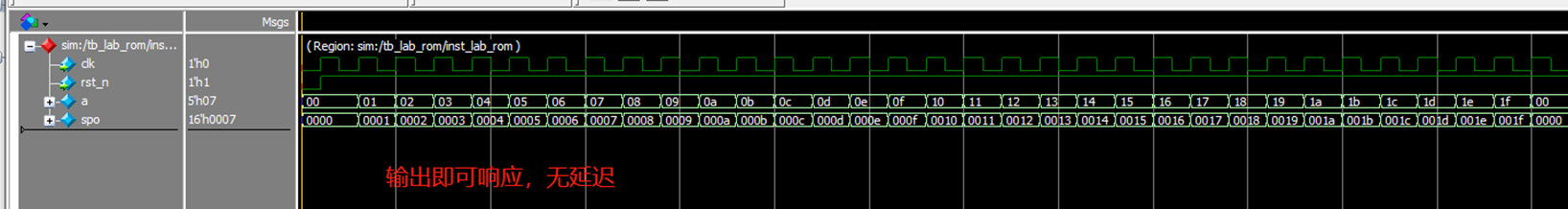

仿真结果

从仿真来看,确实用Distributed Memory Generator生成的ROM IP核是无延迟的。

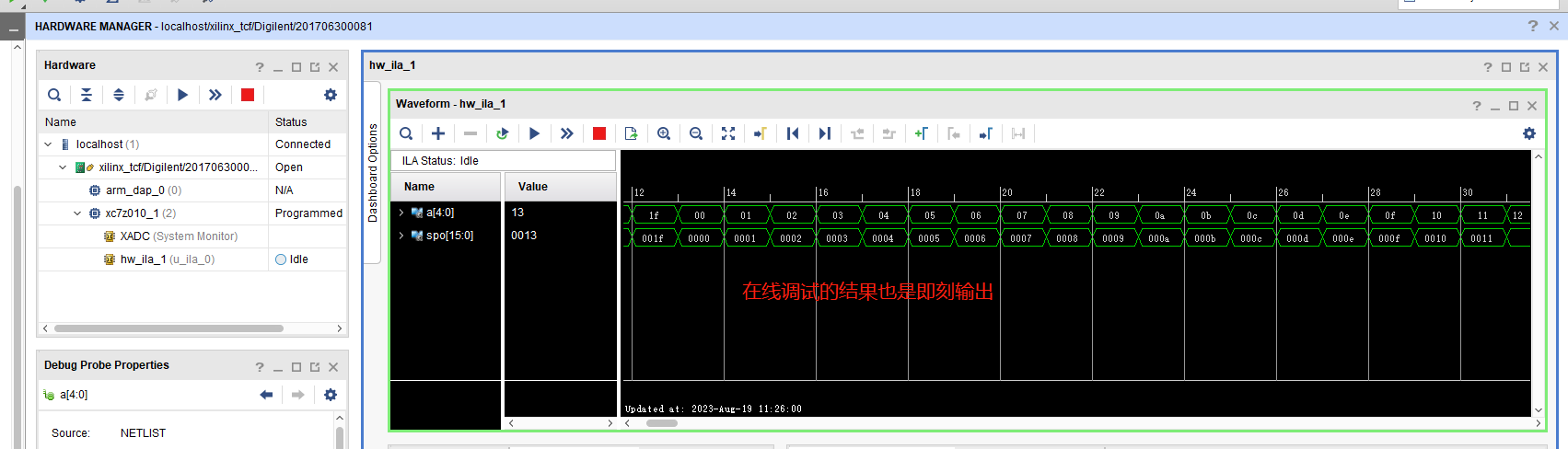

3 在线调试

在线调试的ILA步骤我这里就不赘述了。 我直接给出结果。

总得来讲,Distributed Memory Generator,虽然深度必须是16的倍数,但其生成的ROM IP核输出是无延迟的,真香!