【FPGA/D6】

2023年7月25日

- VGA控制器 视频23

- note

- code

- tb

- 条件编译

- error

- 时序图保存与读取??

- RGBTFT显示屏 视频24

- PPI

- 未分配的引脚或电平的解决方法

VGA控制器 视频23

note

MCU单片机

VGA显示实时采集图像

行消隐/行同步/场同步/场消隐

CRT:阴极射线管

640x480:25MHz(刷新率为60帧80052560=25.2M≈25M)

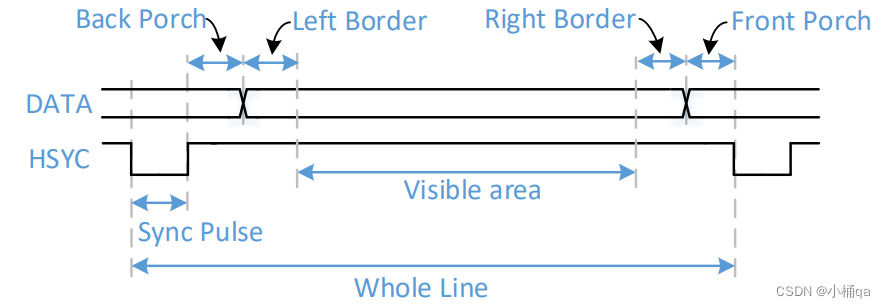

行扫描时序图

场扫描时序图

行同步脉冲的开始位置HS_begin0

行同步脉冲的结束位置HS_end96(pclk)

行数据开始输出的位置Hdat_begin96+40+8=144

行数据开始输出的位置Hdat_end96+40+8+640=784

行同步信号的结束位置Hsync_end96+40+8+640+8+8=800

场同步脉冲的开始位置VS_begin0

场同步脉冲的结束位置VS_end2(line)

场数据开始输出的位置Vdat_begin2+25+8=35

场数据开始输出的位置Vdat_end2+25+8+480=515

场同步信号的结束位置Vsync_endVdat_end2+25+8+480+2+8=525

code

tb

条件编译

条件编译:根据不同的条件来选择对应的HDL文件进行编译以得到对应的逻辑电路

//`define resolution_480x272 1

`define resolution_640x480 1

`ifdef resolution_480x272 `define H_Right_Border `define…........................

`elseif resolution_640x480.......

`endif

源文件里加入`include “vga_pameter.v”

不需要的注释掉

error

输出RGB存在zzzz,时序图光标到zzz,vivado就卡住(data赋给RBG,后者没定义前者相同的位宽)

时序图保存与读取??

vivado一个项目里不能同时打开两个时序图

RGBTFT显示屏 视频24

PPI

PPI:每英寸屏幕所拥有的像素数,相同分辨率的显示屏越小越清晰

未分配的引脚或电平的解决方法

问题:[DRC NSTD-1] Unspecified I/O Standard: 4 out of 4 logical ports use I/O standard (IOSTANDARD) value ‘DEFAULT’, instead of a user assigned specific value. This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all I/O standards. This design will fail to generate a bitstream unless all logical ports have a user specified I/O standard value defined. To

allow bitstream creation with unspecified I/O standard values (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks NSTD-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: a, b, out, and sel.

[DRC UCIO-1] Unconstrained Logical Port: 4 out of 4 logical ports have no user assigned specific location constraint (LOC). This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all pin locations. This design will fail to generate a bitstream unless all logical ports have a user specified site LOC constraint defined. To allow bitstream creation with unspecified pin locations (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks UCIO-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: a, b, out, and sel.

xdc文件开头加入:

set_property SEVERITY {Warning} [get_drc_checks NSTD-1]

set_property SEVERITY {Warning} [get_drc_checks RTSTAT-1]

set_property SEVERITY {Warning} [get_drc_checks UCIO-1]