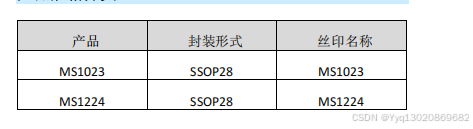

MS1023/MS1224——10MHz 到 80MHz、10:1 LVDS 并串转换器(串化器)/串并转换器(解串器)

产品简述

MS1023 串化器和 MS1224 解串器是一对 10bit 并串 / 串并转

换芯片,用于在 LVDS 差分底板上传输和接收 10MHz 至 80MHz

的并行字速率的串行数据。起始 / 停止位加载后,转换为负载编

码输出,串行数据速率介于 120Mbps 至 960Mbps 。

上电时,这一对芯片可通过内部产生的 SYNC 样本信号同步

模式进行初始化或者解串器与随机数据同步。通过使用同步模

式,解串器可在特定的、更短的时间参数内建立锁定。

当没有数据传输要求时,芯片可以进入掉电模式。另外,可

以通过设置输出脚为高阻态以避免 PLL 失锁。

MS1023 和 MS1224 的工作温度范围为 -40°C 至 85°C 。

主要特点

◼ 100Mbps 至 800Mbps 串行 LVDS 数据有效负载带宽在

10MHz 至 80MHz 的系统时钟之间

◼ 在 80MHz 输入时,芯片功耗小于 550mW (典型值)

◼ 使用同步模式,可快速锁定时钟

◼ 锁定指示器

◼ 不需要外部单元提供 PLL

◼ SSOP28 封装

◼ 可编程时钟边沿触发

◼ 流向行引脚排序,易于 PCB 版图布局

应用

◼ 无线基站

◼ 底板互连

◼ 数字用户线接入复用器