高速SAR架构ADC选型设计

1、最大摆伏FSR: 0 ~ 4.096V,一般Vref要等于FSR

2、最大频率:根据奈奎斯特采样定理大于2倍的信号频率才够还原信号,所以选择20/50倍更好,

3、最小精度,对于一给定模拟输入,实际数字输出与理论预期输出之间的误差

4、分辨率为满刻度电压值(通常为参考电压值)与刻度数的比值,即Resolution = Vref/2^n

5、信噪比SNR,只考虑量化误差时,SNR=6.02N+1.76dB

6、采样时间,将外部信号采集到保持器中

7、转换时间,将保持器中的信号进行量化

8、吞吐率/转换速率/采样率等于采样时间加转换时间,即ADC内部模数转化的速率,

9、LSB,刻度数的一格

10、量化误差,用数字量表示模拟量所引起的误差;分辨率越高,量化误差越小;

11、有效位数ENOB,不仅仅考虑量化误差,且考虑包含谐波失真等影响的非理想情况的信噪比下反推出来的位数

12、传输方式,差分(两根线,抗共模干扰能力强),单端(简单,地为零信号,抗共模干扰能力弱)

13、模拟输入钳位保护

14、抗混叠模拟滤波器

15、微分线性误差

16、积分线性误差

17、偏移误差

18、增益误差

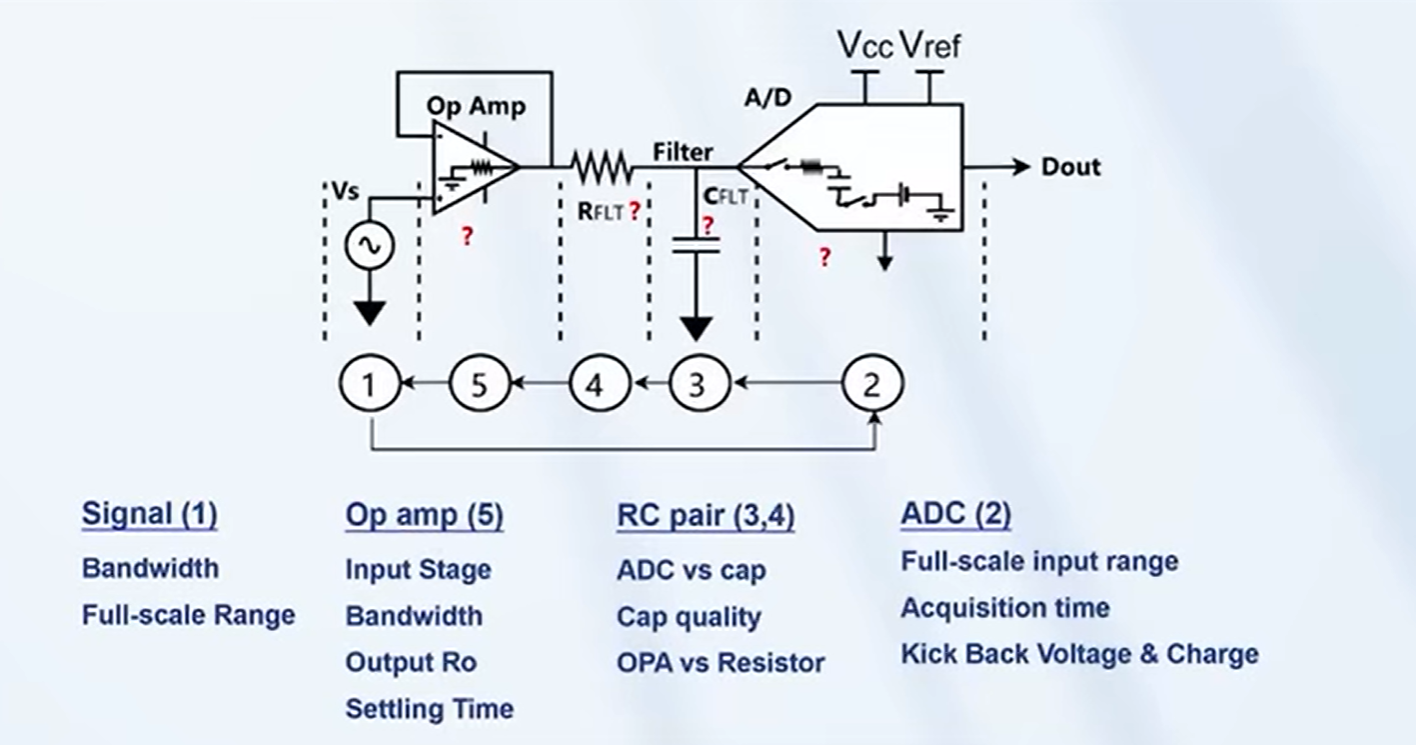

设计的流程:

1、根据信号最小分辨率的需求确定出ADC的位数,即选择ADC(根据传输速率选择ADC架构,比如SAR架构,还有速率慢的Pipeline型,Sigma-delta型);

2、根据ADC选择外部电容的值(经验值一般外部的滤波电容为20倍的内部采样保持电容,为了性能可以选择高规格的电容,比如C0G);

3、根据滤波电容的值及ADC本身的采样时间计算出滤波电阻的值(电阻值根据RC时间常数计算);

4、根据滤波电容、电阻的值计算出运放的增益带宽积GBWP(运放的带宽一般是RC滤波的带宽的4倍),然后进一步的验证看运放的稳定性会不会有什么影响;