PCB 混合介质叠层:材料特性匹配与性能提升的技术解析

在高速电子系统中,PCB混合介质叠层设计通过融合不同特性的材料,实现性能与成本的精准平衡。这种技术通过在同一基板中组合高频低损耗材料(如PTFE、碳氢陶瓷复合材料)与常规FR-4基材,满足5G通信、车载雷达、AI服务器等场景的严苛需求。

一、混合介质叠层的核心原理

混合介质叠层的本质是通过材料特性的差异化配置优化信号传输。高频信号层通常采用低介电常数(Dk)和低损耗因子(Df)的材料,例如Rogers RO4350B(Dk≈3.48)或PTFE(Dk≈2.2),以降低信号衰减和相位失真。而低速信号层或电源层则使用FR-4(Dk≈4.3),在保证基本绝缘性能的同时显著降低成本。这种设计需要解决三大关键挑战:

介电常数不匹配

当信号从高Dk材料(如FR-4)进入低Dk材料(如PTFE)时,特性阻抗会发生跳变。例如,Dk从4.3降至2.2时,50Ω传输线的阻抗可能升至70Ω以上,导致信号反射和畸变。解决方法包括采用渐变式过渡结构(如锥形介质填充)或通过3D场仿真工具(如Ansys HFSS)优化线宽参数。

热膨胀系数(CTE)差异

FR-4的CTE约为14-16ppm/°C,而PTFE仅为3-5ppm/°C。温度变化时,这种差异可能引发层间应力,导致焊点开裂或信号通道断裂。通过在介质交界处填充环氧树脂+氧化铝陶瓷填料的过渡层,可将Z轴CTE差值压缩至<5ppm/°C,有效化解物理失配风险。

模式转换噪声

信号在不同介质层间传输时,可能从TEM模式转换为TE/TM模式,引入额外损耗。通过采用共面波导(CPWG)或带状线结构,可减少非理想模式转换,例如在28GHz频段将串扰抑制至-60dB以下。

二、混合介质叠层的实现流程

1.设计阶段:电磁仿真与材料选型

信号路径定位:通过HFSS等工具识别高频信号区域(如车载雷达板的微带线区),仅在该区域嵌入高频材料,减少70%的高频基材用量。

材料组合策略:高频层选用低Dk材料(如PTFE),低速层采用FR-4,电源层可搭配高Dk材料(如陶瓷填充FR-4)以优化电源完整性。

2.制造阶段:精密层压与工艺控制

分段压合工艺:先将高频材料与铜箔预层压,再与FR-4进行最终压合。通过控制温度(180-200℃)、压力(300-400psi)和时间(60-90分钟),确保层间结合力与厚度均匀性,同时避免PTFE材料的分层风险。

激光微槽定位:采用UV激光切割FR-4基板(精度±25μm),在高频模块与FR-4之间预留0.1mm间隙填充树脂,形成应力缓冲层。

3.测试验证:多维度性能评估

阻抗一致性测试:使用时域反射仪(TDR)和矢量网络分析仪(VNA)验证阻抗精度,确保单端阻抗误差≤±5%,差分阻抗误差≤±7%。

热冲击试验:在-40℃至125℃循环测试中,混合介质板需通过200次以上考验,验证CTE匹配效果。

三、典型应用与技术价值

1.5G基站射频模块

在28GHz毫米波天线设计中,表层使用Dk=2.2的PTFE基材优化信号传播,底层采用Dk=3.48的RO4350B实现阻抗匹配,使插损降低至0.5dB/inch以下,同时成本较全PTFE方案下降40%。

2.车载77GHz雷达板

在L3/L5层微带线区嵌入PTFE模块,结合梯度线宽设计(信号进入高频区时线宽从5mil渐变至3.8mil),有效补偿Dk差异,使77GHz信号传输损耗较传统FR-4方案降低30%,同时通过Al₂O₃填料提升散热效率30%。

3.AI服务器高速接口

在PCIe 4.0信号层局部嵌入罗杰斯RO3010基材,配合混压结构设计,实现10Gbps信号传输误码率<10⁻¹²,板材成本降低22%,满足AI算力设备的高密度互联需求。

四、技术实践与行业价值

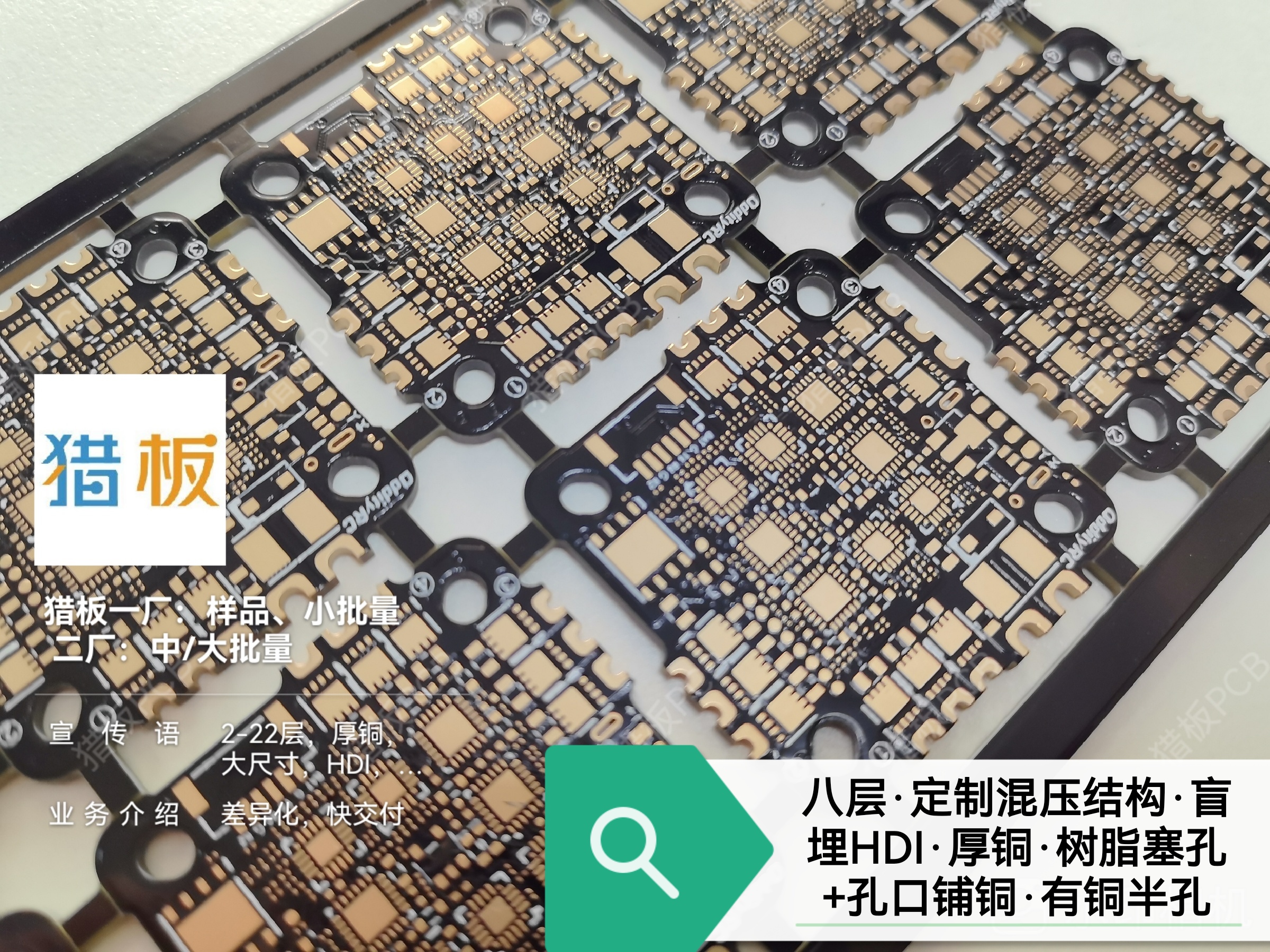

混合介质叠层技术的本质是“按需分配”材料性能,通过科学的仿真设计与精密制造,在成本可控的前提下突破单一材料的性能极限。猎板PCB的实践显示,通过局部化材料重构(在16层板中仅对20%-30%的关键区域使用高频材料),可实现综合成本降低18%;同时,基于基材数据库与算法匹配压合参数,能将介电损耗降低40%,压合周期缩短30%。

作为行业技术演进的缩影,这类实践不仅是高频高速电路的必然选择,更是推动电子制造向精准化、智能化发展的重要支撑。猎板PCB的探索也为混合介质叠层技术的规模化应用提供了可借鉴的路径。