Verilog *2* SPI-立创逻辑派G1测试-1

经过上一篇文章Verilog *1* SPI-发,我们已经通过仿真把这个搞出来了,但是实际上在电路上是啥样还没看过,不动手的话总归还是纸上谈兵,仿真只是为了让搞实际电路更快一点,切不可本末倒置。

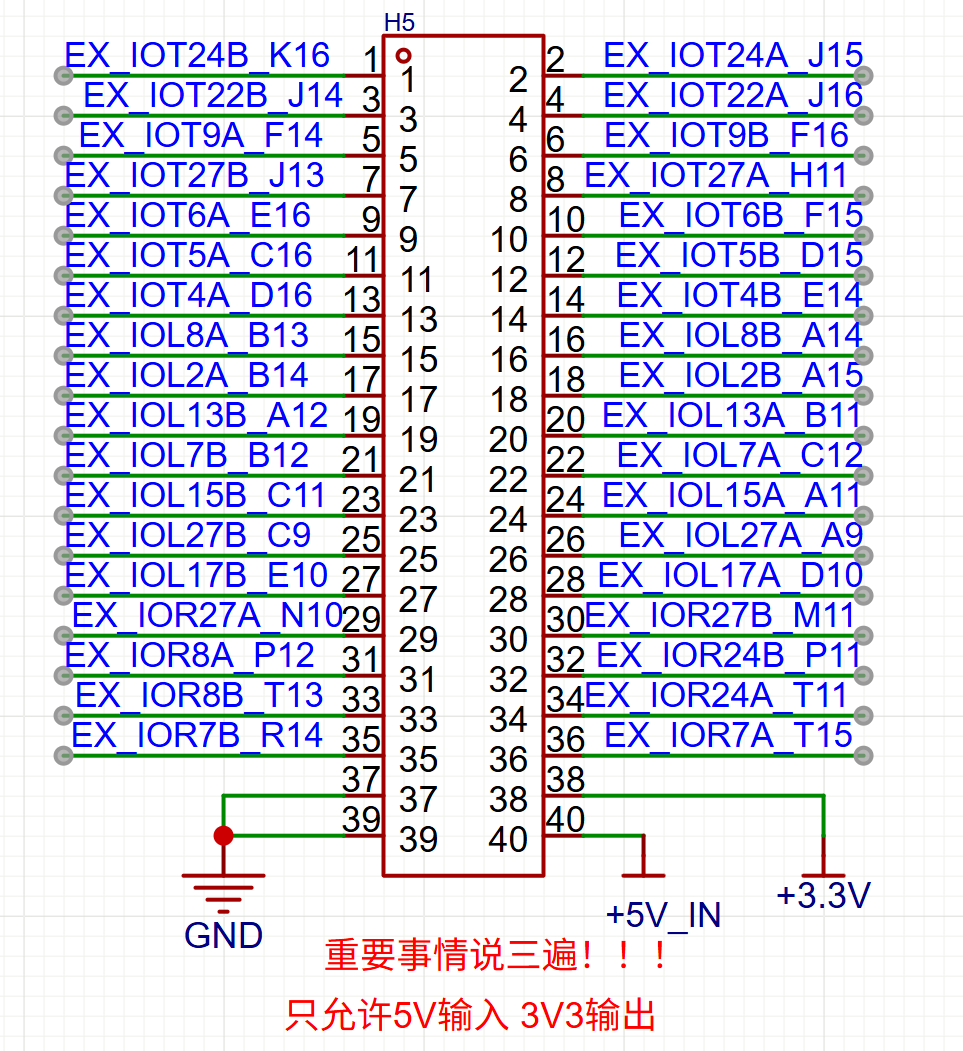

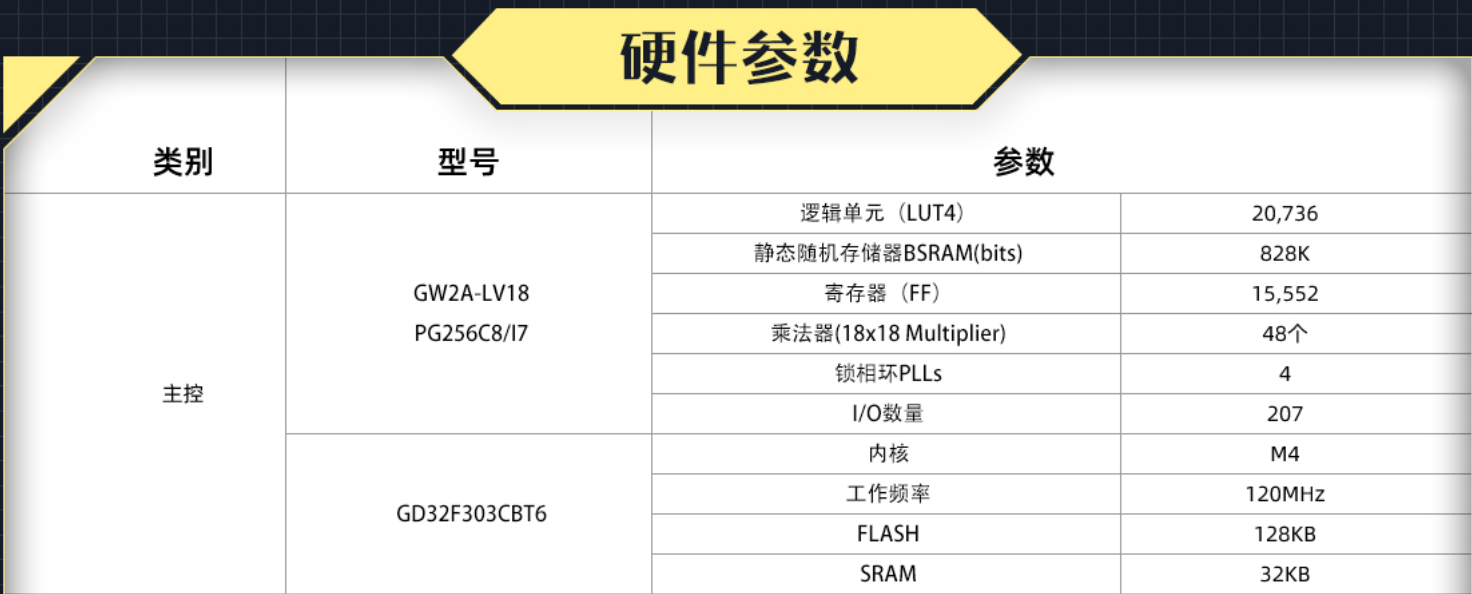

首先我们看一下逻辑派G1的图纸,以下是JLC的逻辑派G1的图纸,用网页可以直接打开。但在这里方便大家查看,我截个图,如图1所示。

https://pro.lceda.cn/editor#id=61327d881e5f4f0c834908cf28c3eb08,tab=1199dcbe5a844fe5a8a074140edc99f8|*1199dcbe5a844fe5a8a074140edc99f8@61327d881e5f4f0c834908cf28c3eb08

图1:FPGA引出的IO

有了图1,咱们就可以开整了!

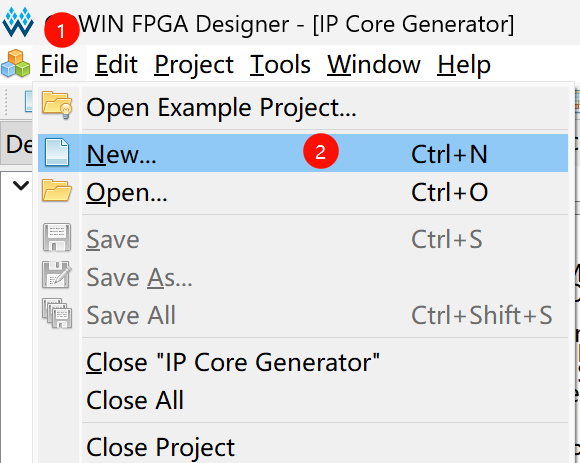

新建工程

File->New

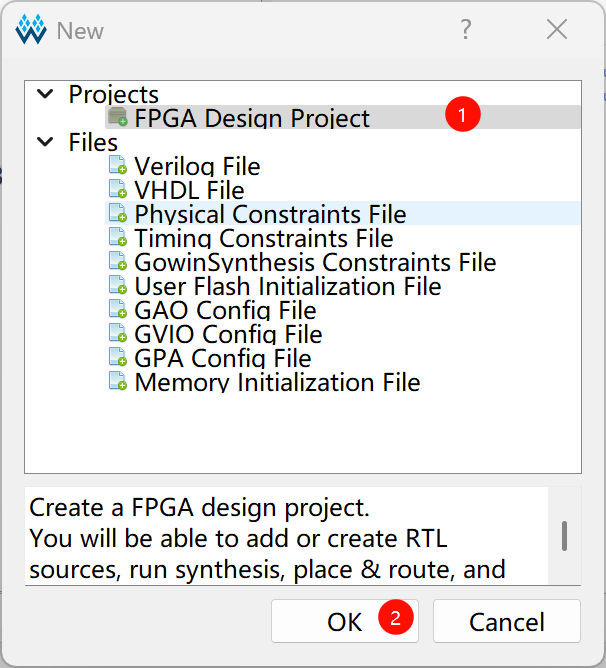

FPGA Design Project ->OK

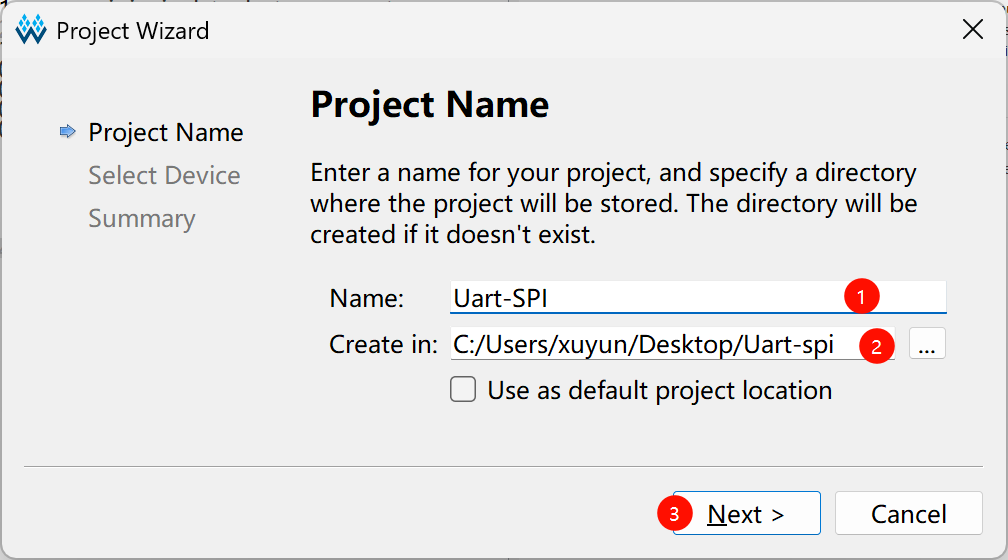

1.Name->取个名

2.Create in -> 文件地址

3.OK

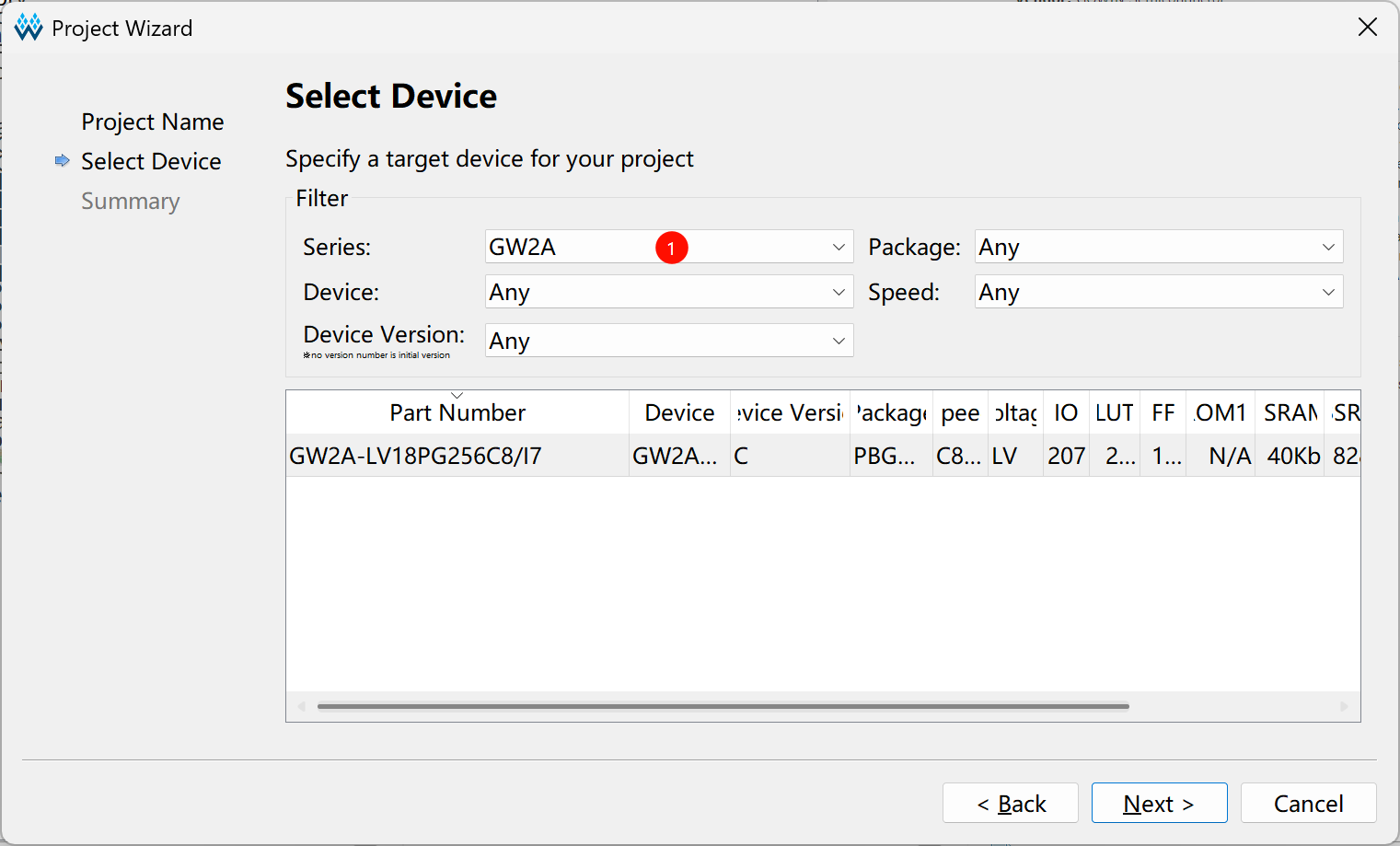

接下来是选型:

截止目前 GW2A下面就一个型号,选择完以后直接Next工程建立完成。

拷贝代码

module SPI (input clk,input rst,input transFlag,output reg cs,output reg mosi,output reg sclk

);// 定义状态

// localparam 只在模块内有效,`define 是全局有效

localparam IDLE = 1'b1;

localparam Trans = 1'b0;reg [1:0] Current_S;

reg [1:0] Next_S;

reg [4:0] Trans_Cnt;

reg [1:0] sclk_status;

reg [7:0] Data;

reg [4:0] clk_div_cnt; // 时钟分频计数器

reg spi_clk; // 分频后的时钟信号// 25 倍时钟分频逻辑

always @(posedge clk or negedge rst) begini