FPGA自学——二选一多路选择器

FPGA自学——二选一多路选择器

文章目录

- FPGA自学——二选一多路选择器

- 一、使用工具

- 二、软件使用

- 一)对界面的了解

- 二)创建新工程

- 三)创建HDL文件

- 四)查看verilog文件

- 三、二选一多路器功能编写

- 一)实现图表:

- 二)实现功能要求:

- 三)代码实现

- 四)分析RTL

- 五)测试文件编写

- 六)仿真

- 七)波形分析

一、使用工具

vivado2018.3

二、软件使用

一)对界面的了解

二)创建新工程

1.点击create project,并点击next

2.修改文件名称+路径,以及对应的注意事项

3.选择RTL工程

4.选择芯片

5.核对信息,创建工程

三)创建HDL文件

1.新建Verilog文件

2.选择编写verilog代码

- constraints : 管脚约束,物理相关信息

- design sources : verilog代码 || 第三方提供的网表文件 ……

- simulation sources : 创建仿真文件

3.创建新的.v文件

4.verilog文件命名

5.添加成功

6.选择引脚,跳过即可

四)查看verilog文件

三、二选一多路器功能编写

一)实现图表:

二)实现功能要求:

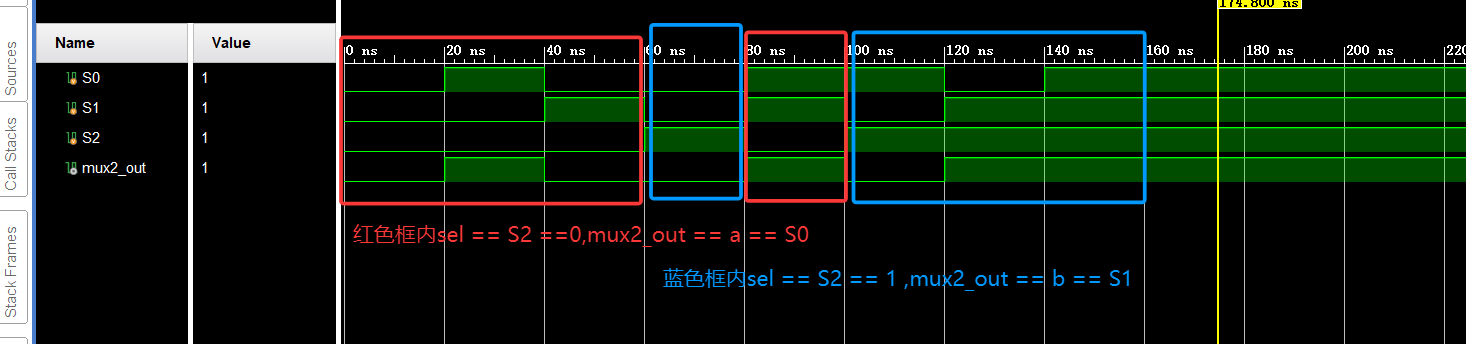

当 sel == 0 时 ,out == a

当 sel == 1 时 ,out == b

三)代码实现

module mux2(a ,b ,sel ,out

);input a ;input b ;input sel ;output out ;//赋值语句 assignassign out = (sel == 0) ? a : b ;endmodule

四)分析RTL

五)测试文件编写

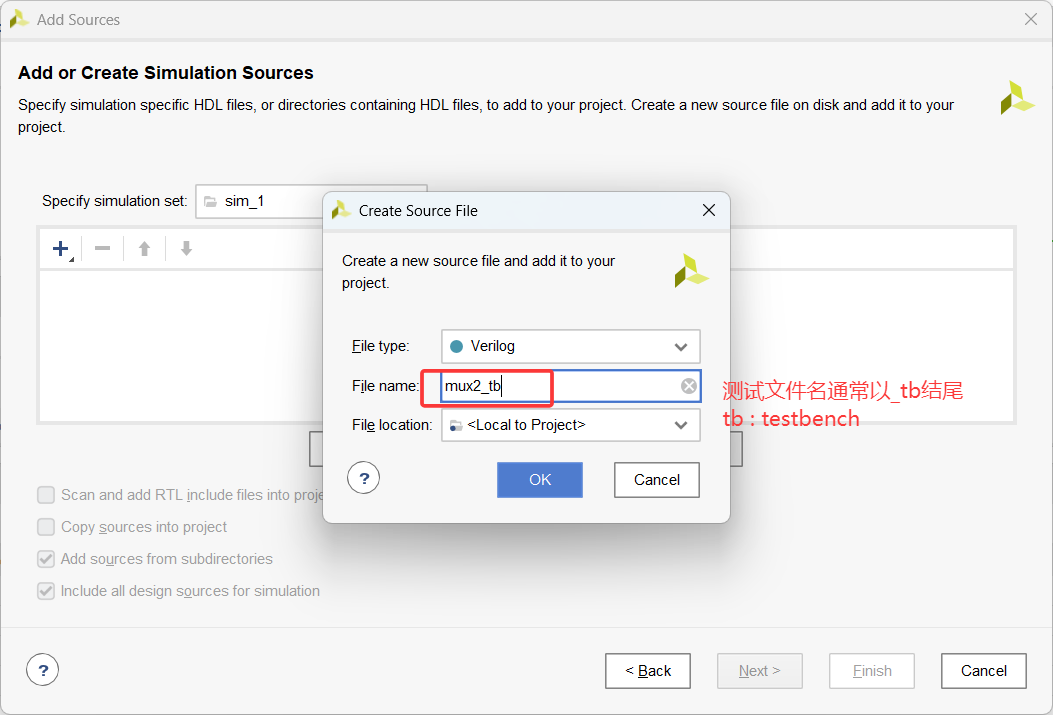

1.创建测试文件

2.测试文件的编写

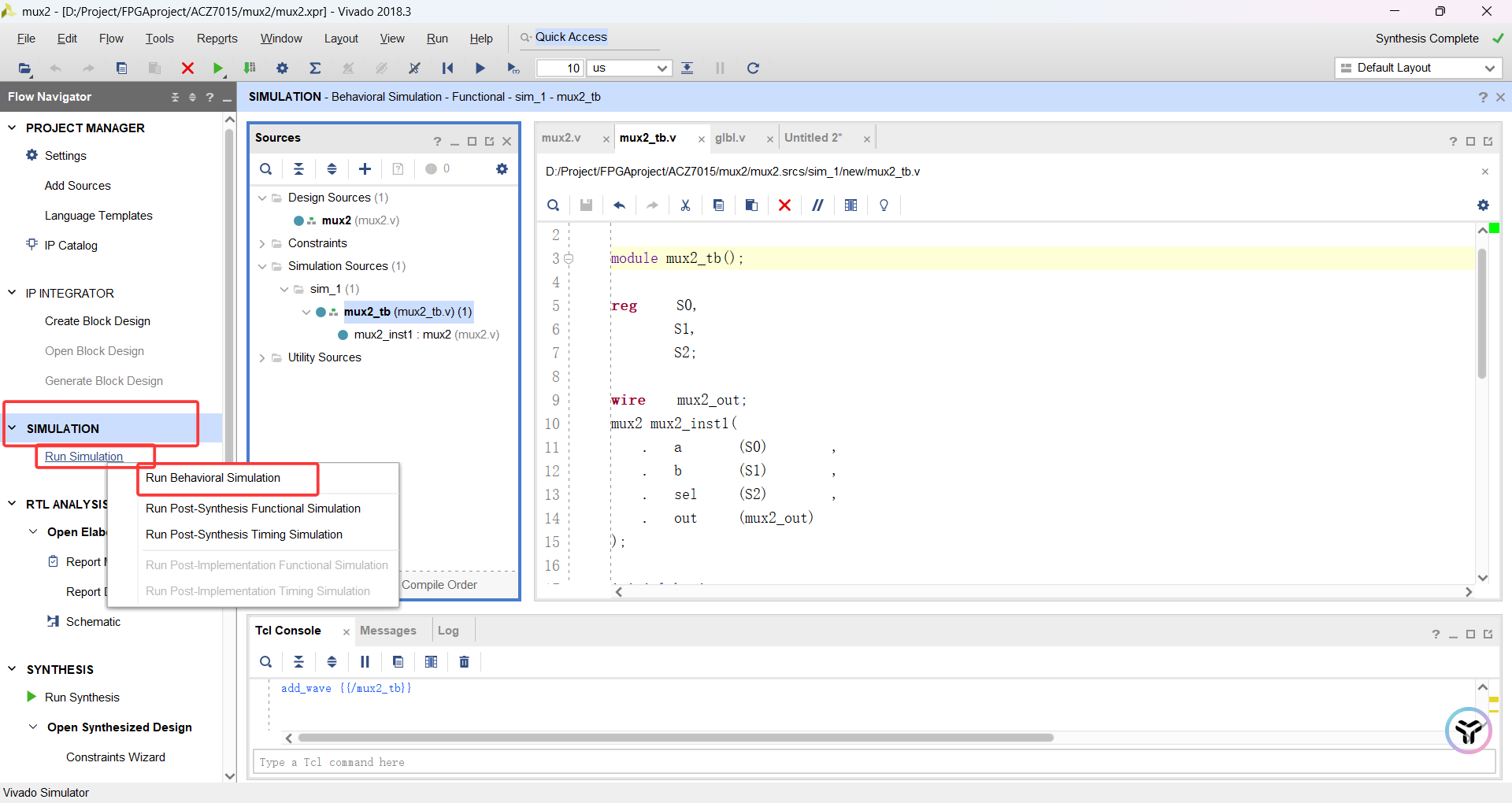

`timescale 1ns / 1ns //时间精度module mux2_tb(); //不需要端口名称reg S0,S1,S2;wire mux2_out;

//例化

mux2 mux2_inst1(. a (S0) ,. b (S1) ,. sel (S2) ,. out (mux2_out)

);//产生激励信号

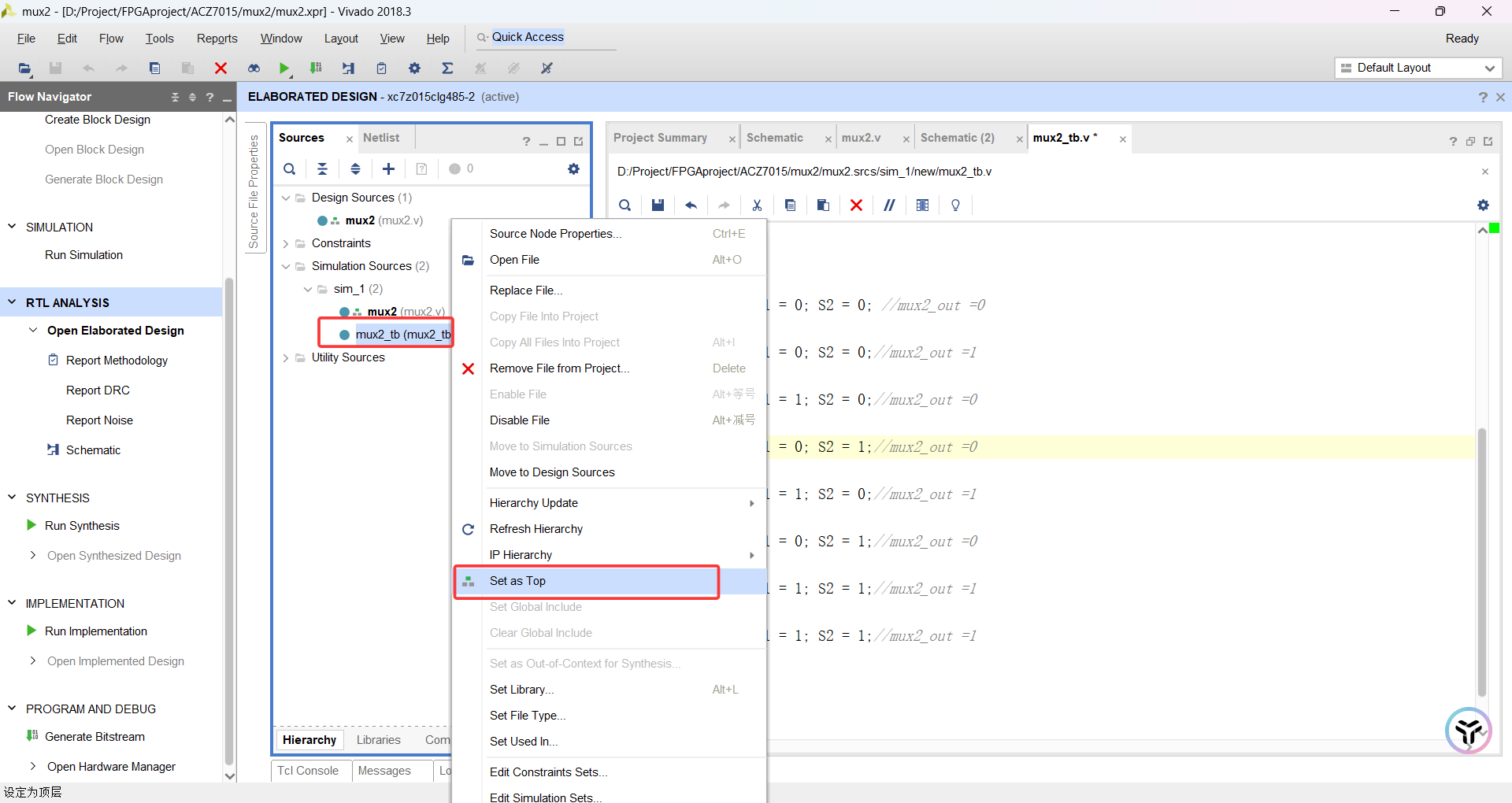

initial begin//a b selS0 = 0; S1 = 0; S2 = 0;//mux2_out =0#20 //时间间隔描述S0 = 1; S1 = 0; S2 = 0;//mux2_out =1#20S0 = 0; S1 = 1; S2 = 0;//mux2_out =0#20S0 = 0; S1 = 0; S2 = 1;//mux2_out =0#20S0 = 1; S1 = 1; S2 = 0;//mux2_out =1#20S0 = 1; S1 = 0; S2 = 1;//mux2_out =0#20S0 = 0; S1 = 1; S2 = 1;//mux2_out =1#20S0 = 1; S1 = 1; S2 = 1;//mux2_out =1endendmodule3.设置测试文件为顶层

六)仿真

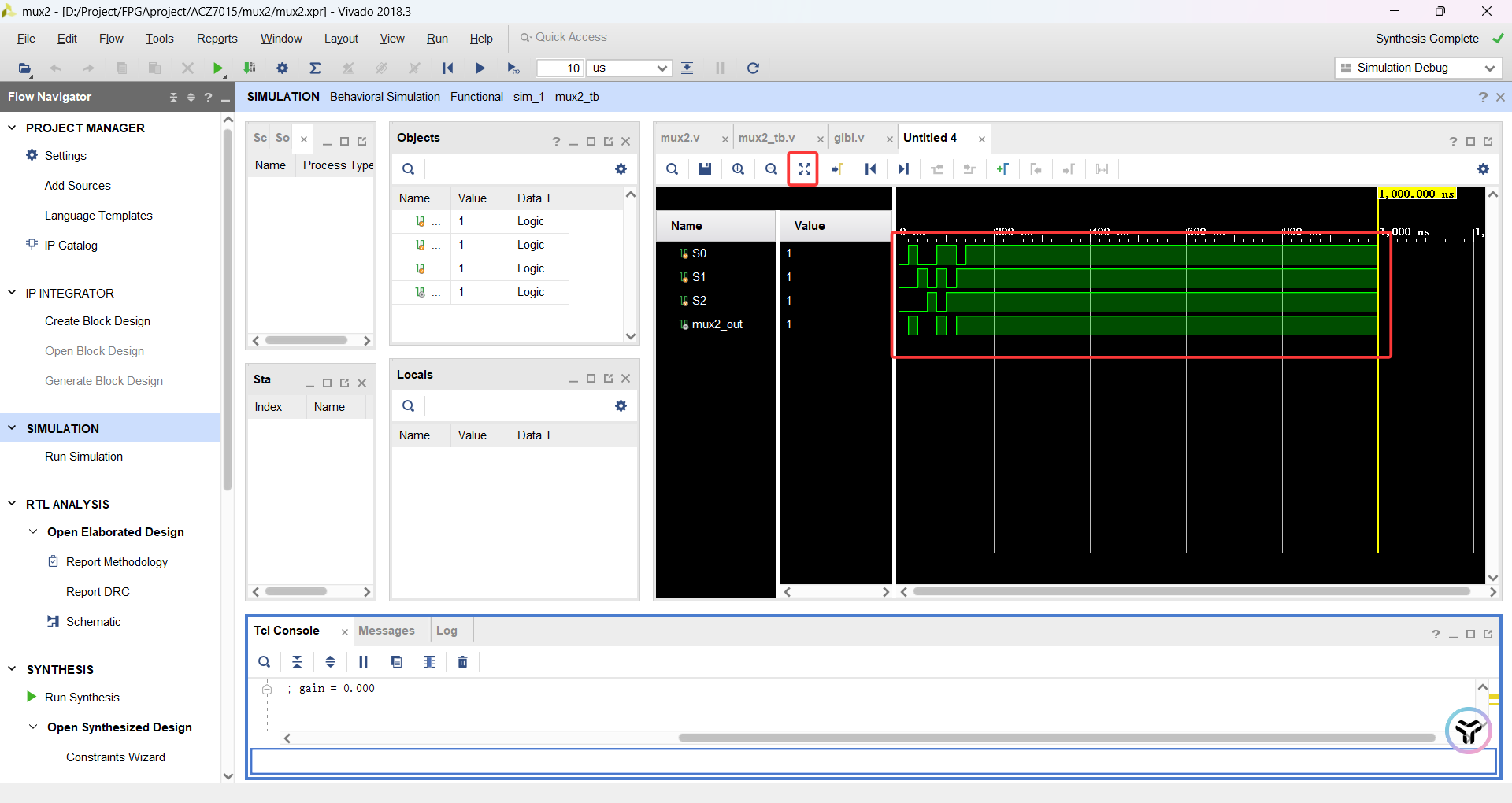

点击全局视图,

七)波形分析

最后仿真的mux2_out结果为:01001011,与期望值相同