LPDDR4x 的 学习总结(3) - SDRAM基本功能

上一节,我们重点介绍了array的存储结构。

本节介绍array周边的电路,对DDR的基本读写操作的相关功能模块的理解。

即通过哪些模块可以实现对ddr的基本读写。最简化的方式是把存储操作理解为行列选择,拆分为横竖两个纬度,最终实现对arrary进行读写。横向有地址选择和竖向对数据的存/取,如下图3.1所示:

图3.1 SRAM cell array功能框图

Address Decoder(横向):地址解码器,使用输入1或0的组合来选择cell的地址,控制输出到1个选择引脚wordline。(相当于input 为 n bits时,输出访问2^n个地址)

Data input/output (竖向):数据的输入/输出是独立引脚时,设计简单。写周期存(input),读周期取(output)。如果为了降低chip面积,可以使用输入输出共享1个引脚,但需要3态buffer来缓存数据。如读周期,使能buffer。

- cell的读写操作

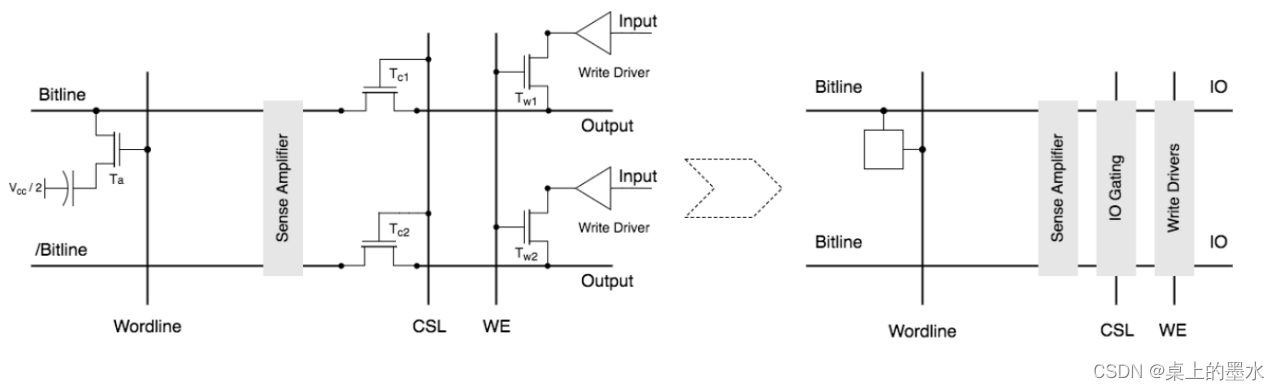

再深入一点,把图3.1细化成图3.2: Precharge(EQ),地址译码和选通,信号敏感放大,IO gating(read mux控制cell连通到外部电路),write driver(写入电路)。

图3.2 DRAM的基本框架

从以上的DRAM cell结构, 可以把逻辑设计对DRAM cell的操作分为3类:

refresh操作:Refresh memory cell

读操作:从memory cell读取数据

写操作:写数据到memory cell

单元电路如何实现refresh,读出和写入?

refresh操作:precharge, access,sense和restore

读操作:precharge, access,sense,restore,IO gating

写操作:precharge, access,sense,restore,IO gating和write driver

即每个操作的过程,包括:precharge, access,sense和restore的过程,当写cell的时候,还需要最后写动作。

1.1.读操作/refresh

2.1.1 Precharge(稳定Vref的电压)

在这个阶段,首先会通过控制 EQ 信号,让 Te1、Te2、Te3 晶体管处于导通状态,将 Bitline 和 /Bitline 线上的电压稳定在 Vref (= Vcc/2)。然后进入到下一个阶段。

2.1.2 Access(cell值电容给Vref充电为Vref+)

经过 Precharge 阶段, Bitline 和 /Bitline 线上的电压已经稳定在Vref 上了,此时,通过控制 Wordline 信号,将 Ta 晶体管导通。Storage Capacitor 中存储正电荷会流向 Bitline,继而将 Bitline 的电压拉升到Vref+。然后进入到下一个阶段。(如果此时cell电容为0,则Vref为放电到Vref-)

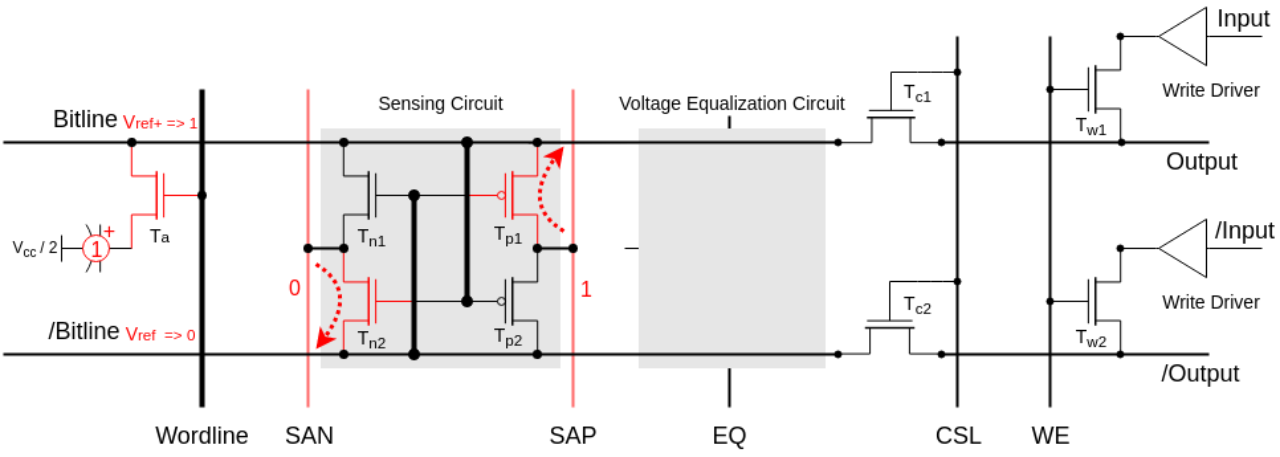

2.1.3 Sense

由于在 Access 阶段,Bitline 的电压被拉升到 Vref+,Tn2 会比 Tn1 更具导通性,Tp1 则会比 Tp2 更具导通性。

此时,SAN (Sense-Amplifier N-Fet Control) 会被设定为逻辑 0 的电压,SAP (Sense-Amplifier P-Fet Control) 则会被设定为逻辑 1 的电压,即 Vcc。由于 Tn2 会比 Tn1 更具导通性,/Bitline 上的电压会更快被 SAN 拉到逻辑 0 电压,同理,Bitline 上的电压也会更快被 SAP 拉到逻辑 1 电压。接着 Tp1 和 Tn2 进入导通状态,Tp2 和 Tn1 进入截止状态。(同理,如果cell为0时,Vref-则会把Tn1和Tp2导通,Bitline的电压会被拉到0电压,/Bitline为电压Vcc)

最后,Bitline 和 /Bitline 的电压都进入稳定状态,正确的呈现了 Storage Capacitor 所存储的信息 Bit。

2.1.4 Restore

在完成 Sense 阶段的操作后,Bitline 线处于稳定的逻辑 1 电压 Vcc,此时 Bitline 会对 Storage Capacitor 进行充电。经过特定的时间后,Storage Capacitor 的电荷就可以恢复到读取操作前的状态。

注:因为WL让电容和sense amp导通后,电子会流出,电容的内容会丢失,这是一种破坏性的读取,所有读出后,还需要存回去。

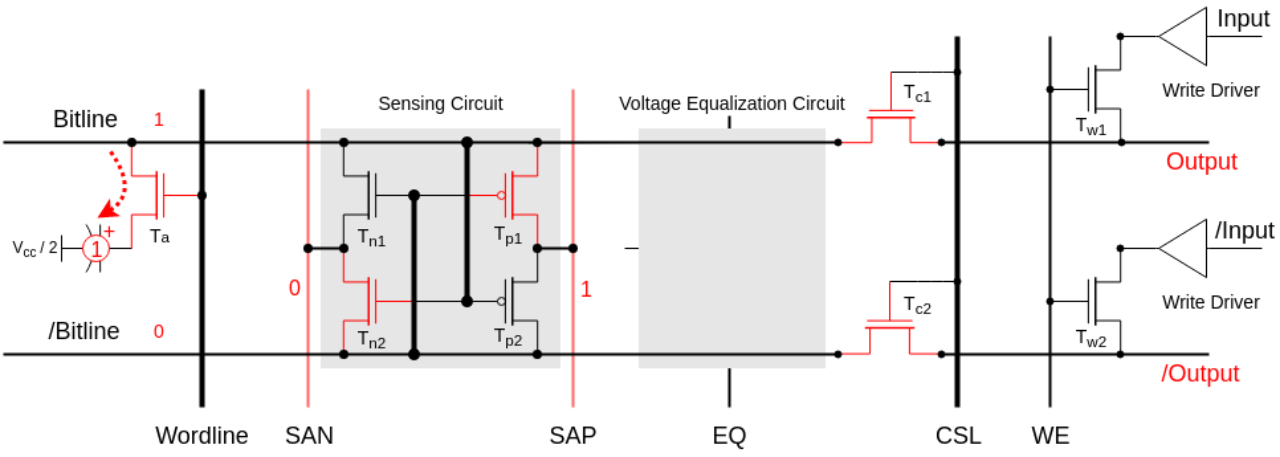

最后,通过 CSL 信号,让 Tc1 和 Tc2 进入导通状态,外界就可以从 Bitline 上读取到具体的信息。

2.1.5 Timing

整个 Read Operation 的时序如下图所示,其中的 Vcc 即为逻辑 1 所对应的电压,Gnd 为逻辑 0。

1.2 写操作

Write Operation 的前期流程和 Read Operation 是一样的,执行 Precharge、Access、Sense 和 Restore 操作。差异在于,在 Restore 阶段后,还会进行 Write Recovery 操作。

1.2.1 Write Recovery

在 Write Recovery 阶段时,通过控制 WE (Write Enable) 信号,让 Tw1 和 Tw2 进入导通状态。此时,Bitline 会被 input 拉到逻辑 0 电平,/Bitline 则会被 /input 拉到逻辑 1 电平。经过特定的时间后,当 Storage Capacitor 的电荷被 Discharge 到 0 状态时,就可以通过控制 Wordline,将 Storage Capacitor 的 Access Transistor 截止,写入 0 的操作就完成了。

参考链接:

- https://web.wpi.edu/Pubs/E-project/Available/E-project-032714-144117/unrestricted/Demonstration_of_SRAM_Design_with_LED_Cube_Display.pdf

- https://www.ndsu.edu/pubweb/~nagong/index_files/conference/C20.pdf

- DRAM 原理 1 :DRAM Storage Cell