[STM32] 5-1 时钟树(上)

文章目录

- 前言

- 5-1 时钟树(上)

- 时钟树的基本介绍

- 时钟树的基本结构

- 大树和小树

- 频率运算简介

- 计数器和分频

- STM32内部结构

- 树的结构于关键节点

- SYSCLK(System Clock) 系统时钟 72M max

- HCLK(AHB Clock) AHB时钟 36M max

- PLCK(APB1 Clock) APB1时钟 36M max

- PLCK2(APB2 Clock) APB2时钟 72M max

- 基本结构:树根\树干

- 树根

- 锁相环

- 锁相环的作用是什么?

- 锁相环的输出信号从哪里来?

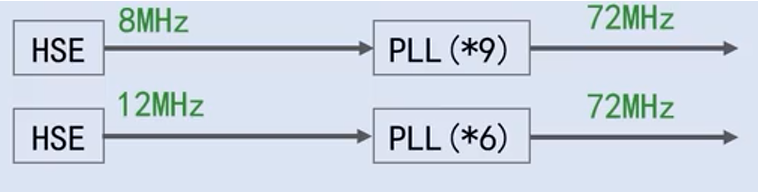

- 尝试将SYSCLK配置为72MHz

前言

-

本笔记内容,为本人依据B站UP主“铁头山羊”视频内容(本人为其粉丝),归纳整理总结而来,如有侵权,联系立即删除,同时有想详细了解的也可进行观看bilibili铁头山羊 。

-

硬件:STM32F103C8T6

-

软件:Keil

5-1 时钟树(上)

时钟树的基本介绍

时钟树的基本结构

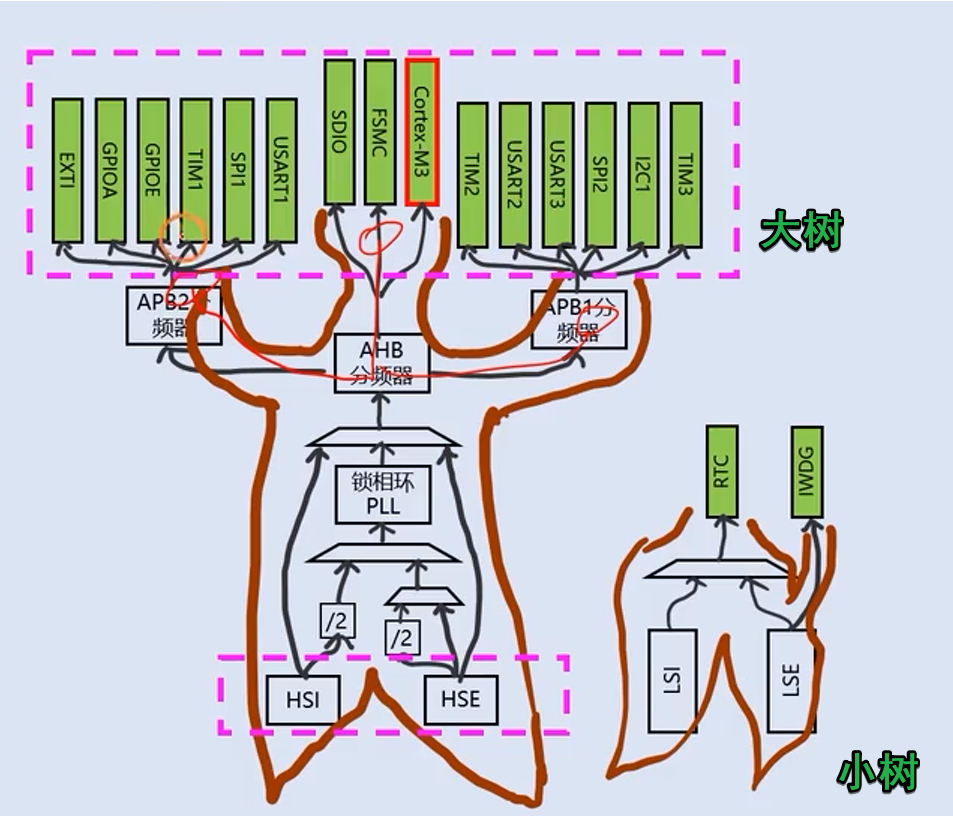

大树和小树

-

大树:主要给 GPIO 等外设提供时钟

-

小树:给 RTC 和 IWDG 供电

(1)RTC:RTC:实时时钟(Real Time Counter);

(2)RTC 的晶振为 32.768kHz =32768Hz = 2^15,经过 2^15 分频后可得到频率为1Hz的时钟,特别适合作为石英表的晶振(经过这样的分频,可以实现数值每秒钟变化1次)。

频率运算简介

-

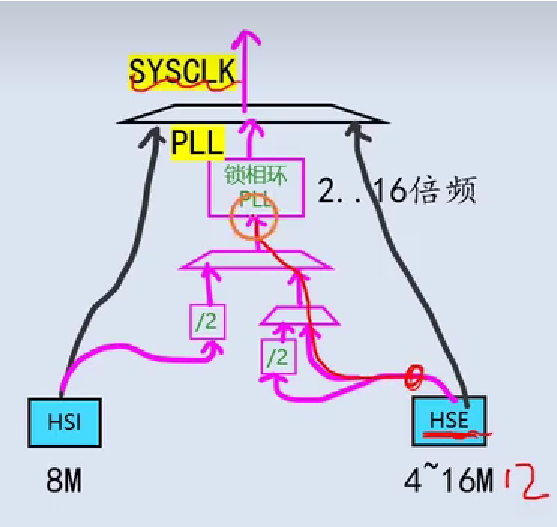

锁相环 PLL:倍频

-

分频器 AHB:分频

-

分频器 APB1/APB2:分频器

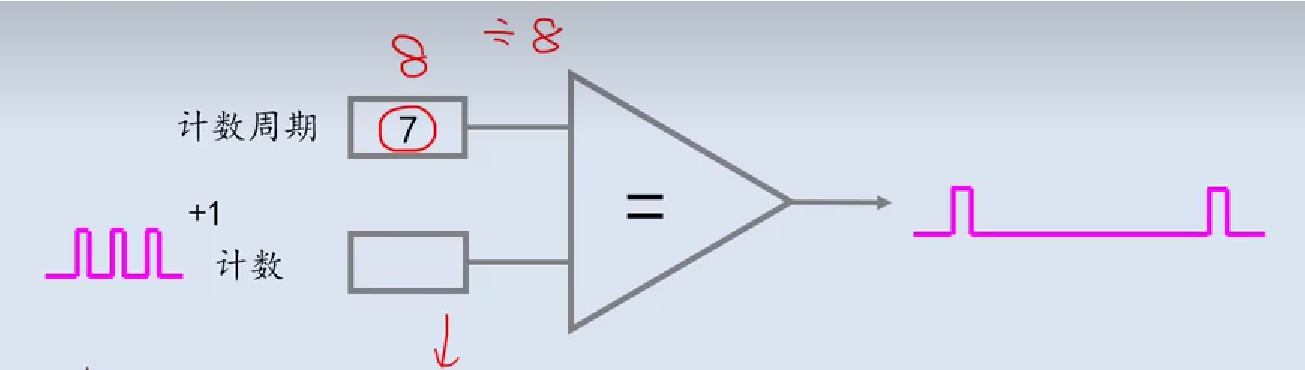

计数器和分频

STM32内部结构

| 总线名称/全称(英文) | 类型 | 频率(MHz) |

|---|---|---|

| AHB(Advanced High Speed Bus) | 系统总线 | 72 |

| APB1(Advanced Peripheral Bus 1) | 外设总线1 | 36 |

| APB2(Advanced Peripheral Bus 2) | 外设总线2 | 72 |

树的结构于关键节点

SYSCLK(System Clock) 系统时钟 72M max

HCLK(AHB Clock) AHB时钟 36M max

PLCK(APB1 Clock) APB1时钟 36M max

PLCK2(APB2 Clock) APB2时钟 72M max

基本结构:树根\树干

树根

| 类型 | 时钟源 | 频率值 |

|---|---|---|

| 高速内部时钟 | HSI | 8 MHz |

| 低速内部时钟 | LSI | 32.768 KHz |

| 高速外部时钟 | HSE | 4-16 MHz(通常 8 MHz) |

| 低速外部时钟 | LSE | 32.768 KHz |

- **终极目的:**产生系统时钟SYSCLK

- 系统时钟的来源:(HSI\ HSE\ PLL)

特点:

(1)SYSCLK 来自 HSI 默认 精度低;

(2)SYSCLK来自锁相环 常用,灵活,范围广;

(3)SYSCLK来自HSE 精度高,频率低。

锁相环

锁相环的作用是什么?

- 做乘法,倍频

锁相环的输出信号从哪里来?

- HIS/2(4M) \HSE\ HSE/2

尝试将SYSCLK配置为72MHz